- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Dear all,

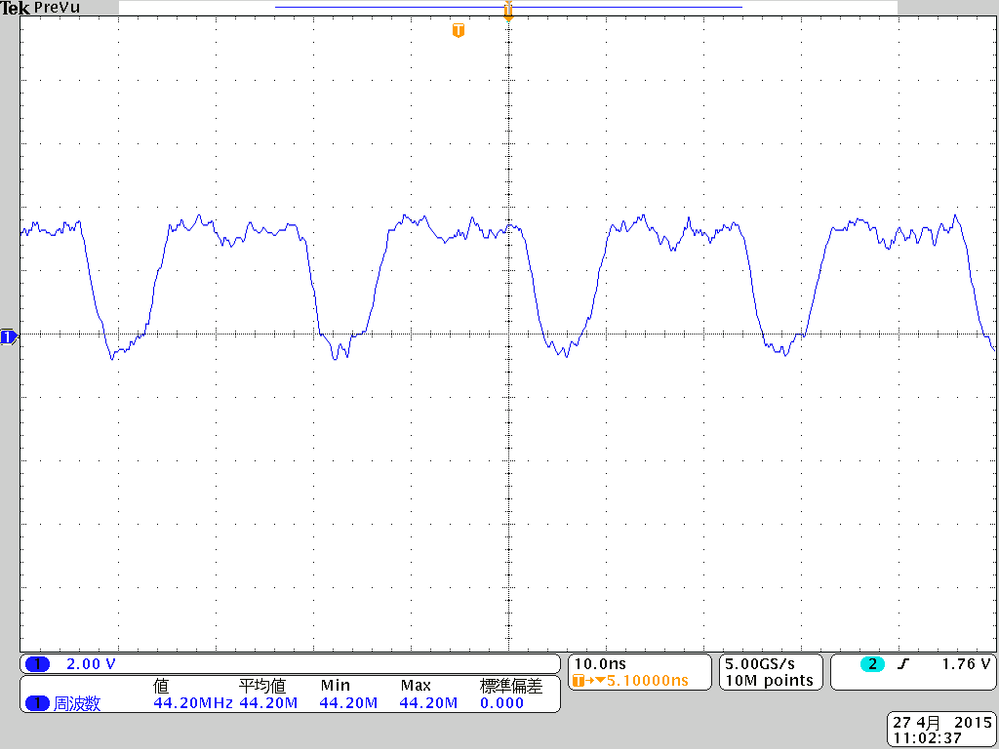

We connect an LCD panel to i.MX25.

LSCLK is 44.3MHz.

A frequency is 44.3MHz of the set value.

However, Duty is not 50%.

Please see the following figure.

Is there the method to change Duty of LSCLK to 50%?

We referred to a reference manual, but were not able to find the method.

Best Regards,

Yuuki

已解决! 转到解答。

Hi Yuuki

duty cycle is not configurable but it can be improved

by using dividers as even numbers (preferably as 2**N) for both

LCDC pixel clock rate divider and LCDC_CLK (PER DIV7).

Also increasing drive strength of clock pad may slightly

improve waveform.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Yuuki

duty cycle is not configurable but it can be improved

by using dividers as even numbers (preferably as 2**N) for both

LCDC pixel clock rate divider and LCDC_CLK (PER DIV7).

Also increasing drive strength of clock pad may slightly

improve waveform.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Dear Igor-san,

Thank you for your support.

We generate LSCLK=44.3MHz from AHB=133MHz.

At this case, we set PERDIV7=0(divided by 1) and PCD=2(divided by 3).

Changing AHB frequency affects the whole system.

Therefore we cannot change the AHB frequency, and PERDIV7 or PCD cannot set even numbers.

In addition, is there the method?

If there is not a method, we have to examine an LCD panel allowing this clock Duty.

Would you tell me the theoretical value of LSCLK Duty in the following setting?

May I have advice?

Best Regards,

Yuuki