- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

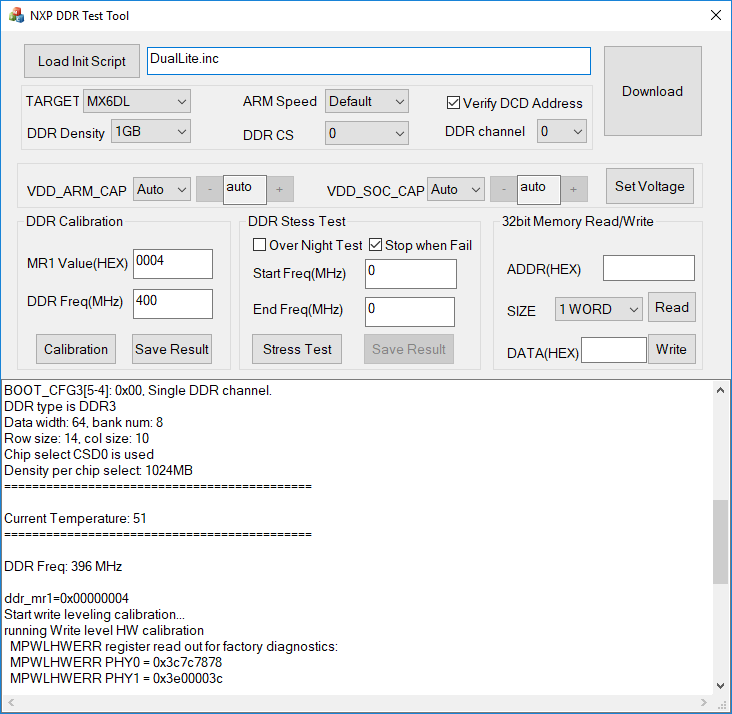

DDR Test tool 1.0.3 pass while 2.92 fail. Which setting is wrong?

Hello,

Some time ago I used DDR_Stress_Tester_V1.0.3 in a custom board without issues. Recently, in a new board I used the same version without issue neither.

I just decided to update the tools to ddr_stress_tester_v2.92 and the application shows HW WL cal status: no suitable delay value found for byte 5 and later Error: failed during write leveling calibration.

Appreciated any suggestion.

Below more details:

BOOT_CFG3[5-4]: 0x00, Single DDR channel. DDR type is DDR3 Data width: 64, bank num: 8 Row size: 14, col size: 10 Chip select CSD0 is used Density per chip select: 1024MB ============================================ Current Temperature: 51 ============================================ DDR Freq: 396 MHz ddr_mr1=0x00000004 Start write leveling calibration... running Write level HW calibration MPWLHWERR register read out for factory diagnostics: MPWLHWERR PHY0 = 0x3c7c7878 MPWLHWERR PHY1 = 0x3e00003c HW WL cal status: no suitable delay value found for byte 5 HW WL cal status: no suitable delay value found for byte 6 Write leveling calibration completed but failed, the following results were found: MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x00430043 MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x0033003B MMDC_MPWLDECTRL0 ch1 (0x021b480c) = 0x001F0024 MMDC_MPWLDECTRL1 ch1 (0x021b4810) = 0x001C001F Write DQS delay result: Write DQS0 delay: 67/256 CK Write DQS1 delay: 67/256 CK Write DQS2 delay: 59/256 CK Write DQS3 delay: 51/256 CK Write DQS4 delay: 36/256 CK Write DQS5 delay: 31/256 CK Write DQS6 delay: 31/256 CK Write DQS7 delay: 28/256 CK Error: failed during write leveling calibration

In other hand, the result using the version 1.0.3 is as below:

DDR_Stress_Tester_V1.0.3\Binary>DDR_Stress_Tester.exe -t mx6x -df "DualLite.inc" MX6DL opened. HAB_TYPE: DEVELOP Image loading... download Image to IRAM OK Re-open MX6x device. Running DDR test..., press "ESC" key to exit. ****************************** DDR Stress Test (1.0.3) for MX6DL Build: Jun 25 2014, 12:09:29 Freescale Semiconductor, Inc. ****************************** =======DDR configuration========== BOOT_CFG3[5-4]: 0x00, Single DDR channel. DDR type is DDR3 Data width: 64, bank num: 8 Row size: 14, col size: 10 Chip select CSD0 is used Density per chip select: 1024MB ================================== What ARM core speed would you like to run? Type 0 for 650MHz, 1 for 800MHz, 2 for 1GHz ARM set to 1GHz Please select the DDR density per chip select (in bytes) on the board Type 0 for 2GB; 1 for 1GB; 2 for 512MB; 3 for 256MB; 4 for 128MB; 5 for 64MB; 6 for 32MB For maximum supported density (4GB), we can only access up to 3.75GB. Type 9 to select this DDR density selected (MB): 1024 Calibration will run at DDR frequency 400MHz. Type 'y' to continue. If you want to run at other DDR frequency. Type 'n' DDR Freq: 396 MHz Would you like to run the write leveling calibration? (y/n) Please enter the MR1 value on the initilization script This will be re-programmed into MR1 after write leveling calibration Enter as a 4-digit HEX value, example 0004, then hit enter 0004 You have entered: 0x0004 Start write leveling calibration Write leveling calibration completed MMDC_MPWLDECTRL0 ch0 after write level cal: 0x00420041 MMDC_MPWLDECTRL1 ch0 after write level cal: 0x0032003A MMDC_MPWLDECTRL0 ch1 after write level cal: 0x001F0024 MMDC_MPWLDECTRL1 ch1 after write level cal: 0x001C001F Would you like to run the DQS gating, read/write delay calibration? (y/n) Starting DQS gating calibration... . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . BYTE 0: Start: HC=0x00 ABS=0x14 End: HC=0x03 ABS=0x48 Mean: HC=0x01 ABS=0x6D End-0.5*tCK: HC=0x02 ABS=0x48 Final: HC=0x02 ABS=0x48 BYTE 1: Start: HC=0x00 ABS=0x18 End: HC=0x03 ABS=0x48 Mean: HC=0x01 ABS=0x6F End-0.5*tCK: HC=0x02 ABS=0x48 Final: HC=0x02 ABS=0x48 BYTE 2: Start: HC=0x00 ABS=0x04 End: HC=0x03 ABS=0x38 Mean: HC=0x01 ABS=0x5D End-0.5*tCK: HC=0x02 ABS=0x38 Final: HC=0x02 ABS=0x38 BYTE 3: Start: HC=0x01 ABS=0x00 End: HC=0x03 ABS=0x34 Mean: HC=0x02 ABS=0x1A End-0.5*tCK: HC=0x02 ABS=0x34 Final: HC=0x02 ABS=0x34 BYTE 4: Start: HC=0x00 ABS=0x7C End: HC=0x03 ABS=0x30 Mean: HC=0x02 ABS=0x16 End-0.5*tCK: HC=0x02 ABS=0x30 Final: HC=0x02 ABS=0x30 BYTE 5: Start: HC=0x00 ABS=0x70 End: HC=0x03 ABS=0x2C Mean: HC=0x02 ABS=0x0E End-0.5*tCK: HC=0x02 ABS=0x2C Final: HC=0x02 ABS=0x2C BYTE 6: Start: HC=0x00 ABS=0x00 End: HC=0x03 ABS=0x24 Mean: HC=0x01 ABS=0x51 End-0.5*tCK: HC=0x02 ABS=0x24 Final: HC=0x02 ABS=0x24 BYTE 7: Start: HC=0x00 ABS=0x58 End: HC=0x03 ABS=0x20 Mean: HC=0x01 ABS=0x7B End-0.5*tCK: HC=0x02 ABS=0x20 Final: HC=0x02 ABS=0x20 DQS calibration MMDC0 MPDGCTRL0 = 0x02480248, MPDGCTRL1 = 0x02340238 DQS calibration MMDC1 MPDGCTRL0 = 0x022C0230, MPDGCTRL1 = 0x02200224 Note: Array result[] holds the DRAM test result of each byte. 0: test pass. 1: test fail 4 bits respresent the result of 1 byte. result 00000001:byte 0 fail. result 00000011:byte 0, 1 fail. Starting Read calibration... ABS_OFFSET=0x00000000 result[00]=0x11111111 ABS_OFFSET=0x04040404 result[01]=0x11111111 ABS_OFFSET=0x08080808 result[02]=0x11111111 ABS_OFFSET=0x0C0C0C0C result[03]=0x11111111 ABS_OFFSET=0x10101010 result[04]=0x11111111 ABS_OFFSET=0x14141414 result[05]=0x11111111 ABS_OFFSET=0x18181818 result[06]=0x11111111 ABS_OFFSET=0x1C1C1C1C result[07]=0x00100010 ABS_OFFSET=0x20202020 result[08]=0x00100000 ABS_OFFSET=0x24242424 result[09]=0x00000000 ABS_OFFSET=0x28282828 result[0A]=0x00000000 ABS_OFFSET=0x2C2C2C2C result[0B]=0x00000000 ABS_OFFSET=0x30303030 result[0C]=0x00000000 ABS_OFFSET=0x34343434 result[0D]=0x00000000 ABS_OFFSET=0x38383838 result[0E]=0x00000000 ABS_OFFSET=0x3C3C3C3C result[0F]=0x00000000 ABS_OFFSET=0x40404040 result[10]=0x00000000 ABS_OFFSET=0x44444444 result[11]=0x00000000 ABS_OFFSET=0x48484848 result[12]=0x00000000 ABS_OFFSET=0x4C4C4C4C result[13]=0x00000000 ABS_OFFSET=0x50505050 result[14]=0x00000000 ABS_OFFSET=0x54545454 result[15]=0x00000000 ABS_OFFSET=0x58585858 result[16]=0x00000000 ABS_OFFSET=0x5C5C5C5C result[17]=0x00000000 ABS_OFFSET=0x60606060 result[18]=0x00000000 ABS_OFFSET=0x64646464 result[19]=0x00000000 ABS_OFFSET=0x68686868 result[1A]=0x00001000 ABS_OFFSET=0x6C6C6C6C result[1B]=0x00011111 ABS_OFFSET=0x70707070 result[1C]=0x01011111 ABS_OFFSET=0x74747474 result[1D]=0x11011111 ABS_OFFSET=0x78787878 result[1E]=0x11111111 ABS_OFFSET=0x7C7C7C7C result[1F]=0x11111111 MMDC0 MPRDDLCTL = 0x40424442, MMDC1 MPRDDLCTL = 0x46444C42 Starting Write calibration... ABS_OFFSET=0x00000000 result[00]=0x11111111 ABS_OFFSET=0x04040404 result[01]=0x00101000 ABS_OFFSET=0x08080808 result[02]=0x00000000 ABS_OFFSET=0x0C0C0C0C result[03]=0x00000000 ABS_OFFSET=0x10101010 result[04]=0x00000000 ABS_OFFSET=0x14141414 result[05]=0x00000000 ABS_OFFSET=0x18181818 result[06]=0x00000000 ABS_OFFSET=0x1C1C1C1C result[07]=0x00000000 ABS_OFFSET=0x20202020 result[08]=0x00000000 ABS_OFFSET=0x24242424 result[09]=0x00000000 ABS_OFFSET=0x28282828 result[0A]=0x00000000 ABS_OFFSET=0x2C2C2C2C result[0B]=0x00000000 ABS_OFFSET=0x30303030 result[0C]=0x00000000 ABS_OFFSET=0x34343434 result[0D]=0x00000000 ABS_OFFSET=0x38383838 result[0E]=0x00000000 ABS_OFFSET=0x3C3C3C3C result[0F]=0x00000000 ABS_OFFSET=0x40404040 result[10]=0x00000000 ABS_OFFSET=0x44444444 result[11]=0x00000000 ABS_OFFSET=0x48484848 result[12]=0x00000000 ABS_OFFSET=0x4C4C4C4C result[13]=0x00000000 ABS_OFFSET=0x50505050 result[14]=0x00000000 ABS_OFFSET=0x54545454 result[15]=0x00000000 ABS_OFFSET=0x58585858 result[16]=0x00000000 ABS_OFFSET=0x5C5C5C5C result[17]=0x00000000 ABS_OFFSET=0x60606060 result[18]=0x00010010 ABS_OFFSET=0x64646464 result[19]=0x00110111 ABS_OFFSET=0x68686868 result[1A]=0x10110111 ABS_OFFSET=0x6C6C6C6C result[1B]=0x11111111 ABS_OFFSET=0x70707070 result[1C]=0x11111111 ABS_OFFSET=0x74747474 result[1D]=0x11111111 ABS_OFFSET=0x78787878 result[1E]=0x11111111 ABS_OFFSET=0x7C7C7C7C result[1F]=0x11111111 MMDC0 MPWRDLCTL = 0x38323032,MMDC1 MPWRDLCTL = 0x34363430 MMDC registers updated from calibration Read DQS Gating calibration MPDGCTRL0 PHY0 (0x021b083c) = 0x02480248 MPDGCTRL1 PHY0 (0x021b0840) = 0x02340238 MPDGCTRL0 PHY1 (0x021b483c) = 0x022C0230 MPDGCTRL1 PHY1 (0x021b4840) = 0x02200224 Read calibration MPRDDLCTL PHY0 (0x021b0848) = 0x40424442 MPRDDLCTL PHY1 (0x021b4848) = 0x46444C42 Write calibration MPWRDLCTL PHY0 (0x021b0850) = 0x38323032 MPWRDLCTL PHY1 (0x021b4850) = 0x34363430 The DDR stress test can run with an incrementing frequency or at a static freq To run at a static freq, simply set the start freq and end freq to the same value Would you like to run the DDR Stress Test (y/n)?

Hi Igor,

Taking in consideration that the board has pass the DDR calibration with version 1.0.3 and also DDR testing under controlled environmental conditions (-10 to 45C) during 24hr (to mention a few), any thought or suggestion regarding this situation with 2.92 version?

I could use previous version and support my production decisions on additional testing, but I would like to be sure I'm not dismissing a possible issue based on the improved new tool revision.

Thanks

Hi Julio

old version did not have ICache and DCache turned on, so newer version provide

more accurate results. You can try to increase WALAT and verify ddr layout with

recommendations given by i.MX6 System Development User’s Guide

https://www.nxp.com/docs/en/user-guide/IMX6DQ6SDLHDG.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hello Igor,

Thanks for your feedback and suggestion.

For the version 1.0.3, I used the guide Freescale i.MX6 DRAM Port Application

Guide – DDR3.

Please, may I know which documentation is available for the 2.92 version?

According with your suggestion, I would need to check further details.

- About the suggested guide, I review it a lot. In other hand, I had been using previous boards (with same layout) without issues.

- About the WALAT suggestion, the default value of WALAT is 1. After set to 2 and 3, the results are similar: no suitable delay value found for byte 5 and 6.

Regards and Thanks,

Julio

After re-check again the post by Oliver Chen at i.MX6/7 DDR Stress Test Tool V2.92, I wondering if the error during my testing has something to do with fix in previous release 2.91:

- Resolved issue with write leveling calibration code where a race condition in the code may result in the calibration routine not being able to find any delay values. Only applies to MX6 series SoCs that support DDR3.