- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

Hi support,

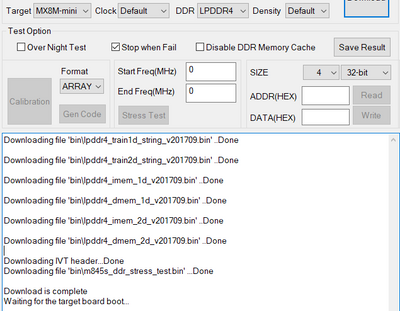

I am developping a iMX8mm board, when I run the ddr tool V3.20, it hangs below.

My PMIC is PCA9450AHN, and the uart configuration is correct.

How can I debug it?

Thanks.

已解决! 转到解答。

Hi everyone,

This issue is fixed, there is something wrong with our hardware design, which makes the CPU enter TEST MODE.

Many thanks to all your support.

Best wishes.

The ddr tool firmware default is for i.MX8MM evk lpddr4 + rohm pmic.

If it is a customized board, at least need to configure the pmic pca.

the guide is on the page.

Have you done that in the .ds file, as you said you have read the guide?

We use the PCA9450 PMIC, and I also add the PMIC configuration in the .ds file as below.

##############step 0.5: configure I2C port IO pads according to your PCB design. #####

########### You can modify the following instructions to adapt to your board PMIC #######

memory set 0x30330214 32 0x00000010 #IOMUXC_SW_MUX_I2C1_SCL

memory set 0x30330218 32 0x00000010 #IOMUXC_SW_MUX_I2C1_SDA

memory set 0x3033047C 32 0x000000C6 #IOMUXC_SW_PAD_I2C1_SCL

memory set 0x30330480 32 0x000000C6 #IOMUXC_SW_PAD_I2C1_SDA

sysparam set pmic_cfg 0x004B

#bit[7:0] = PMIC addr,bit[15:8]=I2C Bus.

#Bus index from 0 ('0' = I2C1, '1' = I2C2, '2' = I2C3, '3' = I2C4)

sysparam set pmic_set 0x2F01

#bit[7:0] = Reg val, bit[15:8]=Reg addr.

#REG(0x2F) = 0x01

sysparam set pmic_set 0x0C02

#REG(0x0C) = 0x02

sysparam set pmic_set 0x171E

#REG(0x17) = 0x1E

sysparam set pmic_set 0x0C00

#REG(0x0C) = 0x00

sysparam set pmic_set 0x2F11

#REG(0x2F)=0x11

The script you have added seems exactly the same as the guide.

You should change to " adapt to your board PMIC"

##############step 0.5: configure I2C port IO pads according to your PCB design. #####

########### You can modify the following instructions to adapt to your board PMIC #######

the guide is just example.

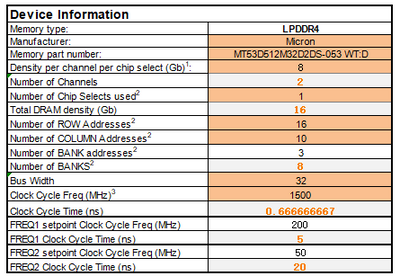

We use the same LPDDR4 configuration as the NXP EVK refrence board.

And I tried to use 1200M, 400M DDR frequency, but it still hangs as below.

Downloading file 'bin\lpddr4_train1d_string_v201709.bin' ..Done

Downloading file 'bin\lpddr4_train2d_string_v201709.bin' ..Done

Downloading file 'bin\lpddr4_imem_1d_v201709.bin' ..Done

Downloading file 'bin\lpddr4_dmem_1d_v201709.bin' ..Done

Downloading file 'bin\lpddr4_imem_2d_v201709.bin' ..Done

Downloading file 'bin\lpddr4_dmem_2d_v201709.bin' ..Done

Downloading IVT header...Done

Downloading file 'bin\m845s_ddr_stress_test.bin' ...Done

Download is complete

Waiting for the target board boot...

The DDR tool always hangs as below.

Downloading file 'bin\lpddr4_train1d_string_v201709.bin' ..Done

Downloading file 'bin\lpddr4_train2d_string_v201709.bin' ..Done

Downloading file 'bin\lpddr4_imem_1d_v201709.bin' ..Done

Downloading file 'bin\lpddr4_dmem_1d_v201709.bin' ..Done

Downloading file 'bin\lpddr4_imem_2d_v201709.bin' ..Done

Downloading file 'bin\lpddr4_dmem_2d_v201709.bin' ..Done

Downloading IVT header...Done

Downloading file 'bin\m845s_ddr_stress_test.bin' ...Done

Download is complete

Waiting for the target board boot...

Download is complete

Waiting for the target board boot...

above, it is only the ddr tool output itself.

It says "Waiting for the target board boot...", because it is waiting on the uart for the board output.

In the tool guide document, there is two keys for ".ds":1. how to configure the uart 2. how to configure the pimc.

It is very to simple to tell the different between the i.MX8MM evk and your board those two keys. then change the ".ds" as you said you have read the guide.

the pmic, you can follow the bsp u-boot spl power init code to set the PCA pmic in ".ds"

After all the bin files are downloaded, which bin will run first? m845s_ddr_stress_test.bin?How to check whether it runs or not?

Downloading file 'bin\lpddr4_train1d_string_v201709.bin' ..Done

Downloading file 'bin\lpddr4_train2d_string_v201709.bin' ..Done

Downloading file 'bin\lpddr4_imem_1d_v201709.bin' ..Done

Downloading file 'bin\lpddr4_dmem_1d_v201709.bin' ..Done

Downloading file 'bin\lpddr4_imem_2d_v201709.bin' ..Done

Downloading file 'bin\lpddr4_dmem_2d_v201709.bin' ..Done

Downloading IVT header...Done

Downloading file 'bin\m845s_ddr_stress_test.bin' ...Done

Download is complete

Thanks. First, I have changed the uart configuration according to our design, second, we use the same PMIC PCA9450 as the EVK board. You mean the example below is not for PCA9450?Then what PMIC is it for?

sysparam set pmic_cfg 0x004B

#bit[7:0] = PMIC addr,bit[15:8]=I2C Bus.

#Bus index from 0 ('0' = I2C1, '1' = I2C2, '2' = I2C3, '3' = I2C4)

sysparam set pmic_set 0x2F01

#bit[7:0] = Reg val, bit[15:8]=Reg addr.

#REG(0x2F) = 0x01

sysparam set pmic_set 0x0C02

#REG(0x0C) = 0x02

sysparam set pmic_set 0x171E

#REG(0x17) = 0x1E

sysparam set pmic_set 0x0C00

#REG(0x0C) = 0x00

sysparam set pmic_set 0x2F11

#REG(0x2F)=0x11

Below is the .ds setting I add for PCA9450 from the spl pmic setting.

sysparam set pmic_cfg 0x0025

#bit[7:0] = PMIC addr,bit[15:8]=I2C Bus.

#Bus index from 0 ('0' = I2C1, '1' = I2C2, '2' = I2C3, '3' = I2C4)

sysparam set pmic_set 0x0C29

#REG(0x0C) = 0x29

sysparam set pmic_set 0x1059

#REG(0x10) = 0x59

sysparam set pmic_set 0x1210

#REG(0x12) = 0x10

sysparam set pmic_set 0x171c

#REG(0x17) = 0x1c

sysparam set pmic_set 0x164a

#REG(0x16) = 0x4a

sysparam set pmic_set 0x22c0

#REG(0x22) = 0xc0

sysparam set pmic_set 0x08a1

#REG(0x08) = 0xa1