- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Processors

- :

- i.MX Processors Knowledge Base

- :

- iMX 8M Mini Register Programming Aid DRAM PLL setting

iMX 8M Mini Register Programming Aid DRAM PLL setting

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

iMX 8M Mini Register Programming Aid DRAM PLL setting

iMX 8M Mini Register Programming Aid DRAM PLL setting

The Register Programming Aid (RPA) provides a default DRAM PLL setting (DRAM frequency) based on the default setting supported in u-boot. It is highly recommended to use the default DRAM frequency settings in the RPA for ease of use and to align with u-boot. Otherwise, in addition to updating the RPA for the new DRAM frequency, the u-boot SPL code itself will need to be manually updated with the new DRAM PLL setting.

Should the user wish to change the DRAM frequency, the following steps are required:

- First, the user needs to update the RPA Register Configuration worksheet tab

Device Information table “Clock Cycle Freq (MHz)“ setting to the desired DRAM frequency

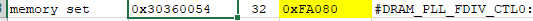

2. Next, in the RPA DDR stress test file worksheet tab search for “memory set 0x30360054”. The address “0x30360054” is for the DRAM PLL register address and its setting needs to be updated to the desired frequency.

Note that there is another place where the DRAM frequency is also updated “freq0 set 0x30360054” but it is automatically updated based on the setting above.

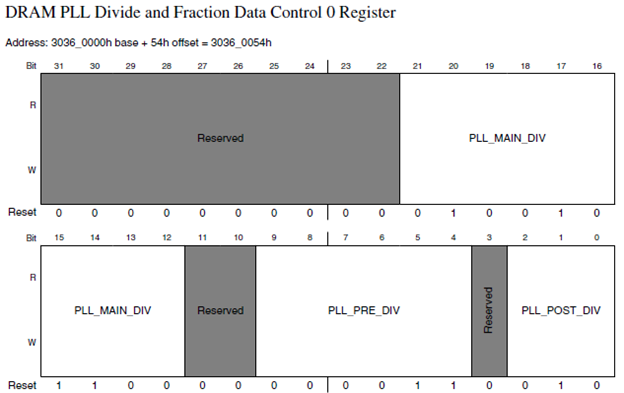

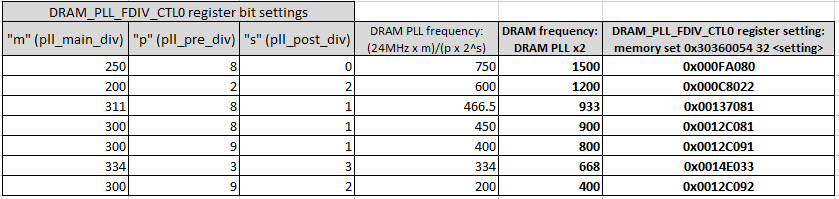

Below is a table of various frequencies to choose from. For frequencies not listed in the table below, it is up to the user to calculate a new register setting based on the formula:

(24MHz x m)/(p x 2^s)

Where “m” represents the PLL_MAIN_DIV, “p” represents the PLL_PRE_DIV, and “s” represents the PLL_POST_DIV.

NOTE: The DRAM frequency is double the DRAM PLL frequency

DRAM_freq = DRAM_PLL x 2

The DRAM PLL register and bit settings are shown below:

The following table provides examples of the various settings to create the desired frequency:

For example, in the i.MX 8M Mini LPDDR4 RPA where the default DRAM frequency is 1500MHz, let’s assume that the user instead wants 1200MHz.

First, the user changes the RPA Register Configuration worksheet tab Device Information table “Clock Cycle Freq (MHz)“ setting to 1200.

Next, in the RPA DDR stress test file worksheet tab search for “memory set 0x30360054” and replace “0xFA080” (original setting from DRAM frequency 1500MHz) with “0x000C8022” (updated for DRAM frequency 1200MHz). Note that for a DRAM frequency of 1200MHz, the DRAM PLL is configured for 600MHz, as the DRAM frequency is double the DRAM_PLL.

The steps outlined above are sufficient in order to create a DDR script for use with the DDR stress test tool to run the calibration and execute the DDR stress test. However, to deploy the generated code in SPL, more steps are needed as the u-boot SPL DDR driver does not automatically change the DRAM PLL according to the generated code. Hence the user will need to manually modify related code in u-boot. It is highly recommended to work with a software engineer familiar with u-boot when making the following modifications.

3. Modify DRAM PLL configuration in uboot-imx/drivers/ddr/imx8m.c, specifically the code highlighted below (function call dram_pll_init). Note that the files and file paths in u-boot change frequently, so if this particular file (or file path) does not exist in the current u-boot, simply search for dram_pll_init or ddr_init.

void ddr_init(struct dram_timing_info *dram_timing)

{

……

debug("DDRINFO: cfg clk\n");

if (is_imx8mq())

dram_pll_init(DRAM_PLL_OUT_800M);

else

dram_pll_init(DRAM_PLL_OUT_750M);

……

}

In the above code, the user should update the macro “DRAM_PLL_OUT_750M” with the new DRAM PLL value. Note that the default DRAM_PLL_OUT_750M results in the DRAM frequency of 1500MHz, where the DRAM frequency is double the DRAM PLL (as previously stated above).

For example, if the user desires to run the DRAM at 1200MHz, they would change the above to: dram_pll_init(DRAM_PLL_OUT_600M);

Note that DRAM_PLL_OUT_600M is a supported macro in the dram_pll_init() API. If the desired DRAM PLL configuration does not exist in dram_pll_init(), you will need to add support in uboot-imx/arch/arm/mach-imx/imx8m.c (as stated above, if this file path does not exist in the current u-boot simply search for dram_pll_init):

void dram_pll_init(enum dram_pll_out_val pll_val)

{

……

}

Related Links

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

On Linux 5.4.24_2.1.0 BSP, there are modifications to step 3.

1. Update the output of the DDR tool replacing:

-#include <asm/arch/imx8m_ddr.h>

+#include <asm/arch/ddr.h>

2. There are several supported frequencies defined at "ddrphy_init_set_dfi_clk" on "drivers/ddr/imx/imx8m/ddrphy_utils.c" If your frequency is already supported you can compile u-boot without any changes.

3. If your new frequency is not supported, you need to change two functions decode_fracpll andddrphy_init_set_dfi_clk, the patch below provides an example of how to add 1866 frequency:

diff --git a/arch/arm/mach-imx/imx8m/clock_imx8mm.c b/arch/arm/mach-imx/imx8m/clock_imx8mm.c

index c44b9777c6..23b88a0762 100644

--- a/arch/arm/mach-imx/imx8m/clock_imx8mm.c

+++ b/arch/arm/mach-imx/imx8m/clock_imx8mm.c

@@ -256,6 +256,8 @@ u32 decode_fracpll(enum clk_root_src frac_pll)

return lldiv((main_div * 65536 + k) * 24000000ULL, 65536 * pre_div * (1 << post_div));

}

+/* imx_int_pll_rate_table format = (PLL Freq, mdiv, pdiv, sdiv, kdiv) */

+/* PLL Freq = [(24MHz * mdiv) / (pdiv * 2^sdiv)] */

static struct imx_int_pll_rate_table imx8mm_fracpll_tbl[] = {

PLL_1443X_RATE(1000000000U, 250, 3, 1, 0),

PLL_1443X_RATE(800000000U, 200, 3, 1, 0),

@@ -263,6 +265,7 @@ static struct imx_int_pll_rate_table imx8mm_fracpll_tbl[] = {

PLL_1443X_RATE(650000000U, 325, 3, 2, 0),

PLL_1443X_RATE(600000000U, 300, 3, 2, 0),

PLL_1443X_RATE(594000000U, 99, 1, 2, 0),

+ PLL_1443X_RATE(466000000U, 311, 8, 1, 0),

PLL_1443X_RATE(400000000U, 400, 3, 3, 0),

PLL_1443X_RATE(266000000U, 266, 3, 3, 0),

PLL_1443X_RATE(167000000U, 334, 3, 4, 0),

diff --git a/drivers/ddr/imx/imx8m/ddrphy_utils.c b/drivers/ddr/imx/imx8m/ddrphy_utils.c

index 7b4ab7c77a..0e81b195e5 100644

--- a/drivers/ddr/imx/imx8m/ddrphy_utils.c

+++ b/drivers/ddr/imx/imx8m/ddrphy_utils.c

@@ -122,6 +122,10 @@ void ddrphy_init_set_dfi_clk(unsigned int drate)

dram_pll_init(MHZ(600));

dram_disable_bypass();

break;

+ case 1866:

+ dram_pll_init(MHZ(466));

+ dram_disable_bypass();

+ break;

case 1600:

dram_pll_init(MHZ(400));

dram_disable_bypass();

4. Once u-boot is compiled you can verify your change by reading 0x30360054 or by booting linux and printing the clocks:

root@imx8mmevk:~# cat /sys/kernel/debug/clk/clk_summary | grep dram

dram_apb 1 1 0 160000000 0 0 50000

dram_alt 0 0 0 100000000 0 0 50000

dram_alt_root 0 0 0 25000000 0 0 50000

dram_pll_ref_sel 1 1 0 24000000 0 0 50000

dram_pll 1 1 0 466500000 0 0 50000

dram_pll_bypass 1 1 0 466500000 0 0 50000

dram_pll_out 1 1 0 466500000 0 0 50000

dram_core_clk 1 1 0 466500000 0 0 50000