- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MXプロセッサ

- :

- i.MXプロセッサ ナレッジベース

- :

- 1866MHz LPDDR4 Porting Guide

1866MHz LPDDR4 Porting Guide

- RSS フィードを購読する

- 新着としてマーク

- 既読としてマーク

- ブックマーク

- 購読

- 印刷用ページ

- 不適切なコンテンツを報告

1866MHz LPDDR4 Porting Guide

1866MHz LPDDR4 Porting Guide

1. Parameter preparation

For more parameter calculation, please refer to: https://community.nxp.com/t5/i-MX-Processors-Knowledge-Base/iMX-8M- Mini-Register-Programming-Aid-DR...

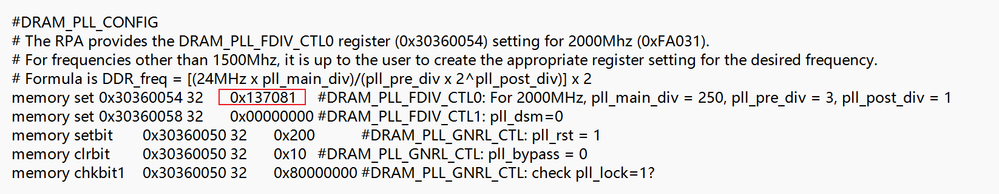

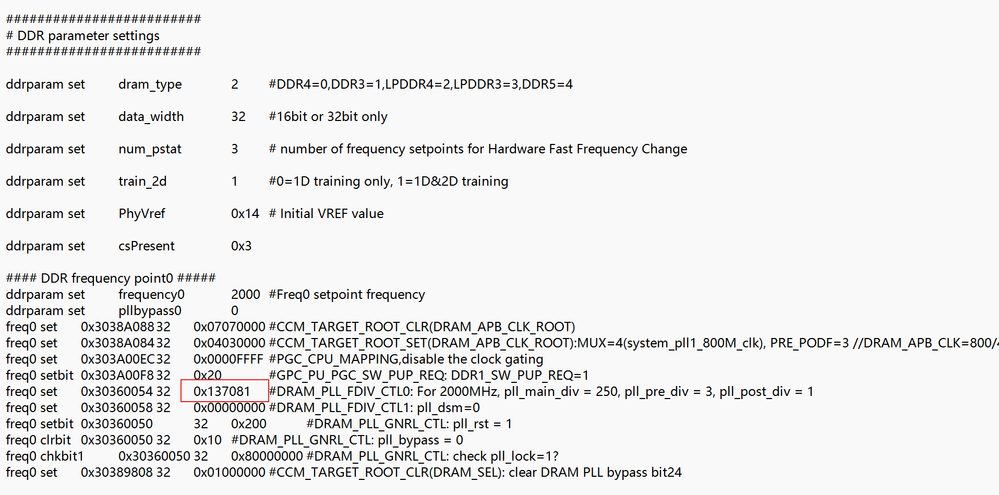

For 1866MHz LPDDR4, we need a DRAM PLL size of 933MHz. The PLL dividing parameters are: m=622,p=16,s=0, k=0.

2. Calibration and stress test with DDR Tool

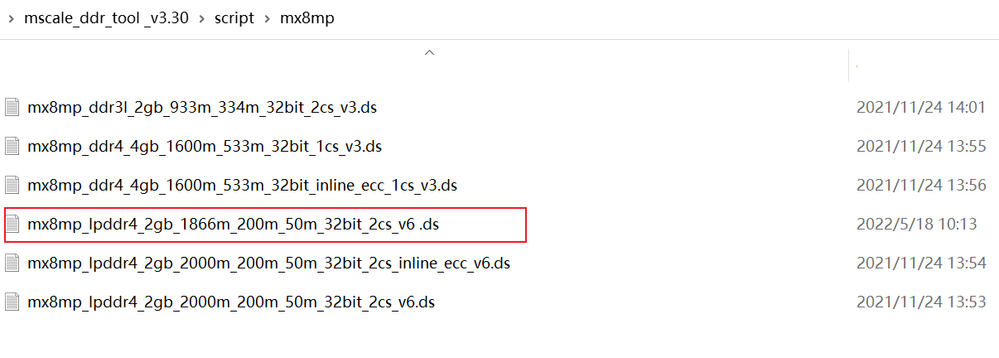

2.1 Creating a test script for 1866MHz

Here we copy the script from another file (e.g. 2000MHz) and modify the contents of the script.

2.2 Modify the script to adapt to 1866MHz

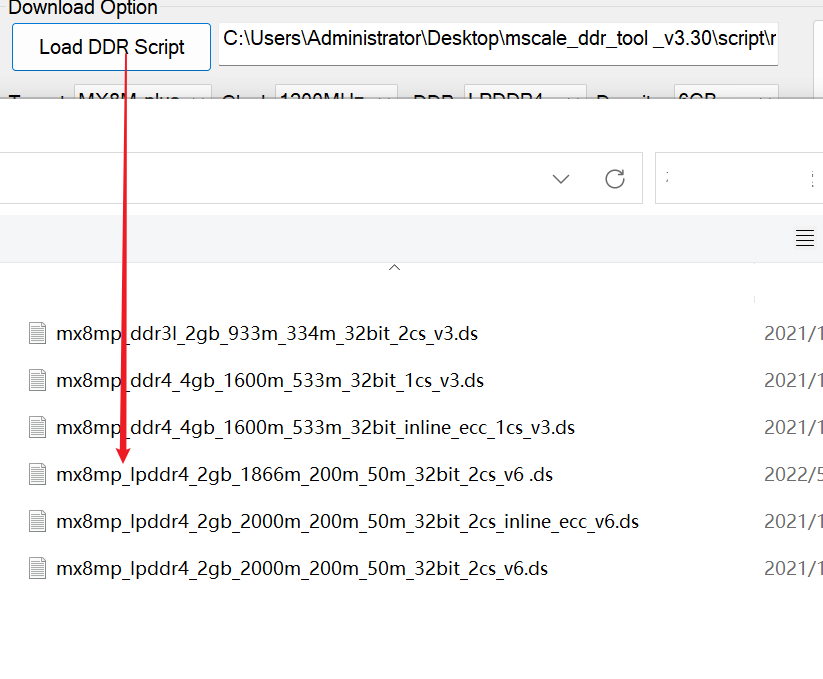

2.3 Download the test script

After selecting the ddr script we created, click on the download button

2.4 Calibrating the stress test

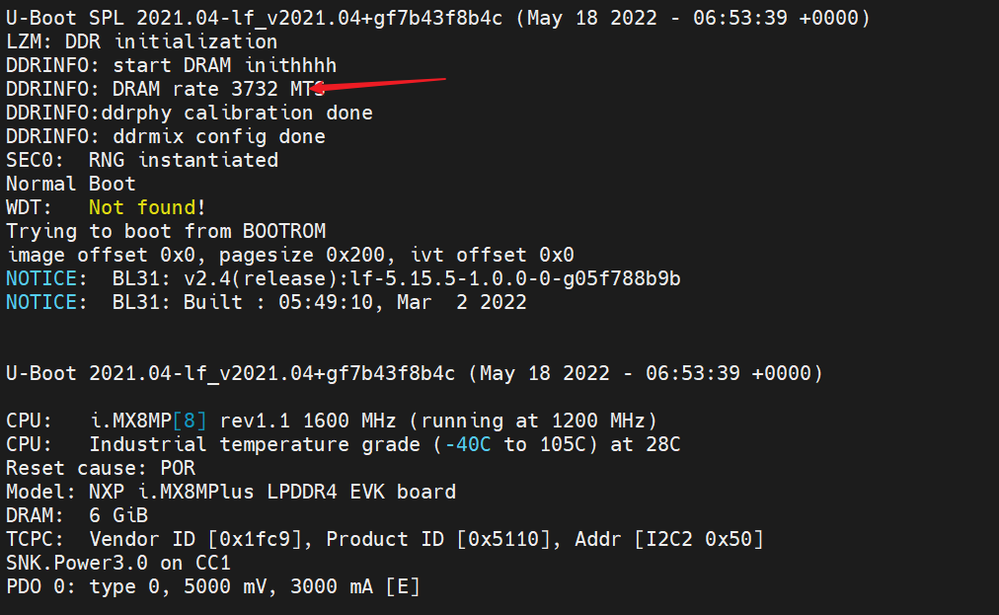

Set the core clock of the chip's cpu to 1.2GHz, then click the Calibration button to calibrate, then click Gen Code to generate the lpddr4_timing.c file. Set the start frequency to 1866MHz for the stress test.

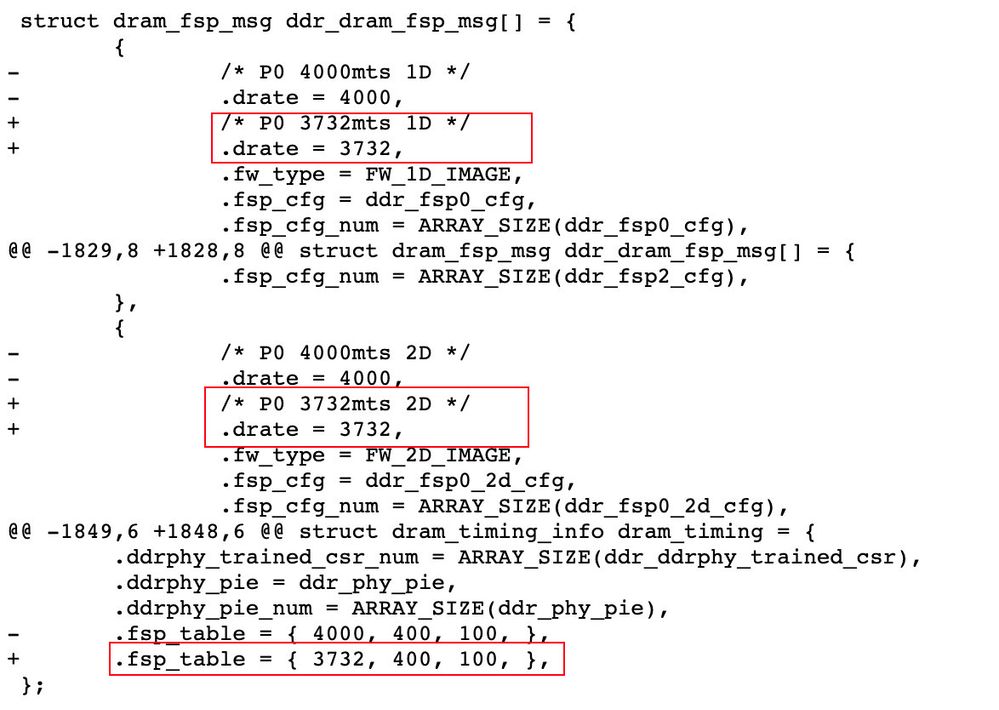

2.5 Modify lpddr4_timing.c

We need to modify the generated lpddr4_timing.c file to change the maximum speed to 3732MTS.

3. SPL patch

After getting the correct lpddr4_timing.c file, the SPL code also needs to be modified to add support for the 933MHz DRAM PLL.

diff --git a/arch/arm/mach-imx/imx8m/clock_imx8mm.c b/arch/arm/mach-imx/imx8m/clock_imx8mm.c

index e39f238fdf...5622a6334e 100644

--- a/arch/arm/mach-imx/imx8m/clock_imx8mm.c

+++ b/arch/arm/mach-imx/imx8m/clock_imx8mm.c

@@ -55,6 +55,7 @@ static struct imx_int_pll_rate_table imx8mm_fracpll_tbl[] = {

PLL_1443X_RATE(650000000U, 325, 3, 2, 0),

PLL_1443X_RATE(600000000U, 300, 3, 2, 0),

PLL_1443X_RATE(594000000U, 99, 1, 2, 0),

+ PLL_1443X_RATE(933000000U, 622, 16, 0, 0),

PLL_1443X_RATE(400000000U, 400, 3, 3, 0),

PLL_1443X_RATE(2660000U, 266, 3, 3, 0),

PLL_1443X_RATE(167000000U, 334, 3, 4, 0),

diff --git a/drivers/ddr/imx/imx8m/ddrphy_utils.c b/drivers/ddr/imx/imx8m/ddrphy_utils.c

index 326b92d784..ebd005bc2b 100644

--- a/drivers/ddr/imx/imx8m/ddrphy_utils.c

+++ b/drivers/ddr/imx/imx8m/ddrphy_utils.c

@@ -117,6 +117,10 @@ void ddrphy_init_set_dfi_clk(unsigned int drate)

dram_pll_init(MHZ(1000));

dram_disable_bypass();

break;

+ case 3732:

+ dram_pll_init(MHZ(933));

+ dram_disable_bypass();

+ break;

case 3200:

dram_pll_init(MHZ(800));

dram_disable_bypass();4. Test results

Reference blog.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

First comment~~~