- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- Vybrid プロセッサ

- :

- PDB & FTM, synchronization of ADC and pulse outputs

PDB & FTM, synchronization of ADC and pulse outputs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

PDB & FTM, synchronization of ADC and pulse outputs

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello!

We have some questions about the FTM and PDB module.

I'm working with the Vybrid VF5xx/VF6xx. The documents I've found (VybridRM, VybridSeries, AN4822) are good but not very clear in every point.

We need a lot of time-synchronized signals. This means:

- ADC channels which are sampled in specific time slots

- DAC channels, also set on specific time

- >10 Timer Outputs (timed output pulses, rising and falling edge controllable, jitter-free)

- input capture

- 8 PWM signals

The FTM's can be synchronized to each other. (RM P.1740)

The PDB can be triggered from the FlexTimer. (Do I need a FTM channel for this? Or can it be done by the way?)

So, everything is synchronized so far.

Now, I can trigger the 2 ADC's with 2 PDB channels, each with up to 8 pretriggers for 8 ADC channels each. (Do I need here an Interrupt to set the next ADC channel for next conversion, or is the PDB able to do it by himself?)

Further, I can trigger the 2 DAC's with 2 more PDB channels.

Is this correct so far?

Now the question: With the PDB (4 remaining channels), it is possible to generate pulse outputs. Can they be connected directly to a GPIO output pin? Or how can it be done?

And for further pulse output signals, is it the only way to generate FTM interrupts and set/clear normal GPIO's in the interrupt routine? And then set a new FTM counter value for the next interrupt? (We have not enough FTM channels for combined PWM signals)

The goal is, to use the CPU as less as possible and to have not a lot interrupts. Is there any better way to generate more than 10 synchronized output pulses? (The pulse frequency is about 50 kHz)

I hope someone has already worked with amd can help us with this modules.

Thanks!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

The PDB can be triggered from the FlexTimer. (Do I need a FTM channel for this? Or can it be done by the way?)

>> The PDB can be triggered by the FTM just like you said and you have to configure the channel that will trigger the PDB.

Now, I can trigger the 2 ADC's with 2 PDB channels, each with up to 8 pretriggers for 8 ADC channels each. (Do I need here an Interrupt to set the next ADC channel for next conversion, or is the PDB able to do it by himself?)

>> The PDB will will trigger the ADC, each pre-trigger needs to be calculated in order that the next conversion of the ADC starts after the first ADC conversion time. But notice that in the RM you have up to 2 ADC modules and the PDB has only 2 pre-triggers per ADC Channel.

In general you have to refer to the Chip Configuration chapter of the RM to make sure about the amount of available channels and the interconnections for each module. Each chapter of the module shows the general design but all the features might be reduced.

For example:

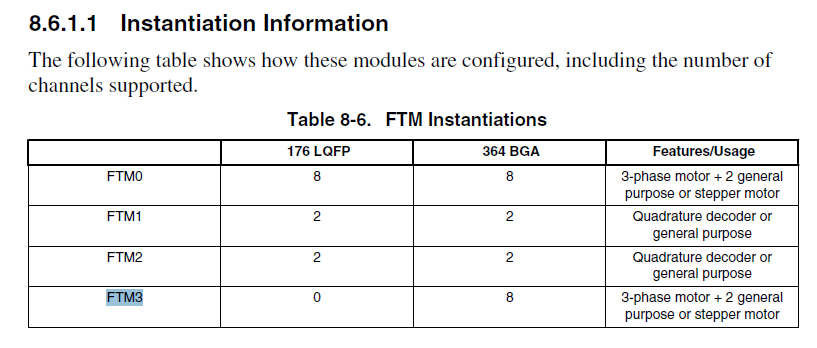

This shows that each PDB module can trigger 2 ADC modules and 2 channels per ADC module. That means that you can schedule 4 ADC channels to be converted. And there is no pulse output of the PDB.

For the FTM:

Then you can have up to 20 FTM channels depending on the package. In case they are not enough you can always use the PIT to trigger DMA transfers and change GPIO pin state.

I hope this helps,

Alejandro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

Our conclusion at the moment is, its not possible to meet our requirements with the Vybrid alone. (other opinions are welcome...)

We are now thinking about a solution with a CPLD involved to generate all the output pulses.

Then, our only question is how to trigger 10 ADC channels without involving the CPU?

Is this setup possible:

- an FTM triggers the PDB, which triggers 4 ADC channels.

- the FTM triggers also 6 ADC's -> the FTM triggers an ADC, which requests a DMA for saving the result, and this DMA requests another DMA channel for loading the next ADC setup to the ADC. (something is described in the AN4590 for Kinetis. Is it the same for Vybrid? or is there a simpler solution for this?)

- the FTM triggers also the extern CPLD with the init trigger (if possible) or a free PWM channel used as clock.

Regards

Benno

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

That seems possible, but I would check the chip configuration in the RM just to make sure of the interconnections of the modules.

You might see that in the module chapters it is explained a full-featured module, but not all the features and interconnection are applied.

I wonder if you want to sample 10 channels at the same time. If so, that won´t be possible, because you will need 10 different ADC modules. Nevertheless you might be able to schedule the 10 conversions at different times.

Regards,

Alejandro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi again

Thanks for your last answers.

We have now a solution for the timing of the ADC's. We have the following chain initialized (with processor expert):

FTM-trigger -> DMA writes channel to ADC -> ADC samples -> DMA writes result to the Memory -> DMA toggles pin(for testing purposes)

If we need more than one ADC sample in the same timeslot, the last DMA (DMA toggles pin) can start the first DMA (DMA writes channel to ADC) again. So its possible, to sample a lot of different ADC channels with a few FTM channels.

And because im writing anyway: In Processor Expert generated file Cpu.c, i can't build the asm lines:

/* Initialize Vector Base Register */

asm("mov r0,%0" : : "r" (&__vector_table));

asm("mcr p15, 0, r0, c12, c0, 0");

Two errors came up: [#18: expected a ")"] and [#549: variable "R0" is used before its value is set]

What are these lines for? i commented the lines out, then building the project is possible.

Thanks

Benno

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

We found the problem with the DMA1. There is a problem in the IO_Map-file, generated by ProcessorExpert...

We are now working on our last problem: We have to show the performance of the vybrid. But we are miles away from the target-performance.

Is there any sample-project, which shows how to set the processor to max. Speed? (Enable and use of L1/L2 caches, use of FPU and NEON, and how i can see this modules are really working...) We are working on it since days, and have no more ideas...

How are the DMIPS measured by Freescale?

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Alejandro

Thanks for your reply.

Its a helpful answer, but not the solution we would like to have...

We have 20 FTM channels. I need 8 of them for PWM generation and one for input capture.

We need at least 12 synchonized pulse outputs, rising and falling edge on dedicated position to each other.

And also more than 4 ADC channels synchronized to the pulse outputs, as also the two DAC's.

How can it be done in a good way?

- The PDB Block, synchronized with the FTM, fires the two DAC's and four ADC's.

Because some ADC's can be sampled in a row, we can use the 'ADC complete interrupt' to set and start a following sampling.

-> Bad, we avoid using interrupts. Is there any possibility for 'ADC scan' or something similar, which scan different ADC channels in a row and save the result without involving the CPU? Problably together with the DMA module?

I find only informations about HW triggered single channel sampling, nothing with incrementing channel number or so.

- Restart the PIT on begin of every new cycle. We have 8 PIT channels, so we can generate 4 output pulses (8 controlled edges) with 8 DMA requests. This edges can only be in the second half of the cycle, otherwise the PIT will occur more than once until they are restarted on begin of next cycle.

- Still we have not enough output compare signals for both-edge controlled output pulses. So we have to generate FTM interrupts and there set GPIO outputs as well the timer value for the next FTM interrupt.

Would this work?

We're not very happy with a solution with so many Interrupts. Are there better options for time-synchonizing without interrupts?

Regards

Benno