- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- Tシリーズ

- :

- Re: 32 bit IFC access of FPGA via GASIC mode

32 bit IFC access of FPGA via GASIC mode

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We are having a customized board with T1022 processor. We have connected FPGA on IFC bus with Chip select 1 of processor , and had done respective settings of GASIC mode in include/configs/T104xRDB.h file along with configuration for board/freescale/t104xrdb/law.c file. Both the files are attached .

When we are accessing the CPLD from u-boot , the u-boot generates an error suggesting to reset the board.

We have also tried to access CPLD in linux, there also the read command throws kernel panic exception.

When we are using logic analyzer inside our FPGA then our state machine is working fine returning the correct data and ready signal at desired time as shown in the GASIC timing diagram in Reference Manual.

When using GASIC write cycle, processor is not driving low on RW signal as observed from Logic Analyzer built inside FPGA.

I am attaching the both log of kernel and uboot crash along with T104xRDB.h (config file) and law.c (Local Access Window file).

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

ufedor the problem is now resolved. We are able to access FPGA via GASIC mode.

The problem was we had disabled parity error in IFC_CSOR1_GPCM, which disables parity checking on received data but parity checking on address is always enabled. Now we have handled that case in our cpld hence the GASIC mode is working now.

I understand there is an option to disable parity checking using bit 2 (PAR_EN) of IFC_CSORn_GPCM register only for data and not for address.

If there is a parity error on address entire , shouldn't the core throw an error instead of crashing. The basic point of parity is to isolate the error so that a wrong cycle is not completed. Is there any setting we are missing to circumvent this ???

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

ufedor Please respond to the above query.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

You wrote:

> One additional information the read happens successfully for first time,

> every time we power on the board but u-boot gives crash log on subsequent reads.

What happens on the IFC during "subsequent" read?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

ufedor the problem is now resolved. We are able to access FPGA via GASIC mode.

The problem was we had disabled parity error in IFC_CSOR1_GPCM, which disables parity checking on received data but parity checking on address is always enabled. Now we have handled that case in our cpld hence the GASIC mode is working now.

I understand there is an option to disable parity checking using bit 2 (PAR_EN) of IFC_CSORn_GPCM register only for data and not for address.

If there is a parity error on address entire , shouldn't the core throw an error instead of crashing. The basic point of parity is to isolate the error so that a wrong cycle is not completed. Is there any setting we are missing to circumvent this ???

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Uncorrectable error during read transaction is reported to the core as error report machine check.

Please check how this error interrupt is processed in your system.

Refer to the e5500 Core Reference Manual, 4.9.3.1 General Machine Check, Error Report, and NMI Mechanism.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks ufedor for the support. Your inputs helped us to debug and solve the problem faced by us.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

As per the hardware team this is the trace of failing read transaction.

What is the difference between traces of the transactions "md.w 0xffdf0000 1" and "md.w 0xffdf0050 1"?

-> No difference. they are two different addresses of FPGA .

One additional information the read happens successfully for first time, every time we power on the board but u-boot gives crash log on subsequent reads.

=> md.l 0xffdf0000 1

ffdf0000: 05050d0d ....

=> md.l 0xffdf0000 1

ffdf0000:Bad trap at PC: 7ff694e0, SR: 9402fb16, vector=e00

NIP: 7FF694E0 XER: 00000000 LR: 7FEF0B6C REGS: 7faedb30 TRAP: 0e00 DAR: 00000000

MSR: 9402fb16 EE: 1 PR: 1 FP: 1 ME: 1 IR/DR: 01

GPR00: 7FF54F90 7FAEDC20 7FAEDEE8 00000009 0000003A 7FAEDAC7 00000020 7FAEDACF

GPR08: 00000000 00000020 FFDF0000 7FAEDC20 7FF057A8 28C12C0B 00000001 00000000

GPR16: 00000004 7FF705C8 00000000 0000002E FFFFFF97 7FF5CC70 00000000 7FF694E0

GPR24: 7FF62D8C 00000009 00000008 FFDF0000 FFDF0000 00000001 7FF752C8 00000004

Call backtrace:

7FF54F90 7FF057D0 7FF1A7C8 7FEFC360 7FEFCB20 7FEFCBD0 7FF191B4

7FEFA440 7FEFD474 7FF4E3D4 7FEFD848 7FEF0F50

Exception in kernel pc 7ff694e0 signal 0

### ERROR ### Please RESET the board ###

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In the provided T104xRDB.h:

> #define CONFIG_SYS_CSOR1 CSOR_GPCM_GPMODE_ASIC

Ensure that the FPGA asserts RDY_L within 256 cycles of IFC module input clocks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

FPGA is asserting RDY_L within 256 cycles of IFC module clocks.

Still we are facing the same issue.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please provide a digital scope or logic analyzer trace corresponding for the failing read transaction.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

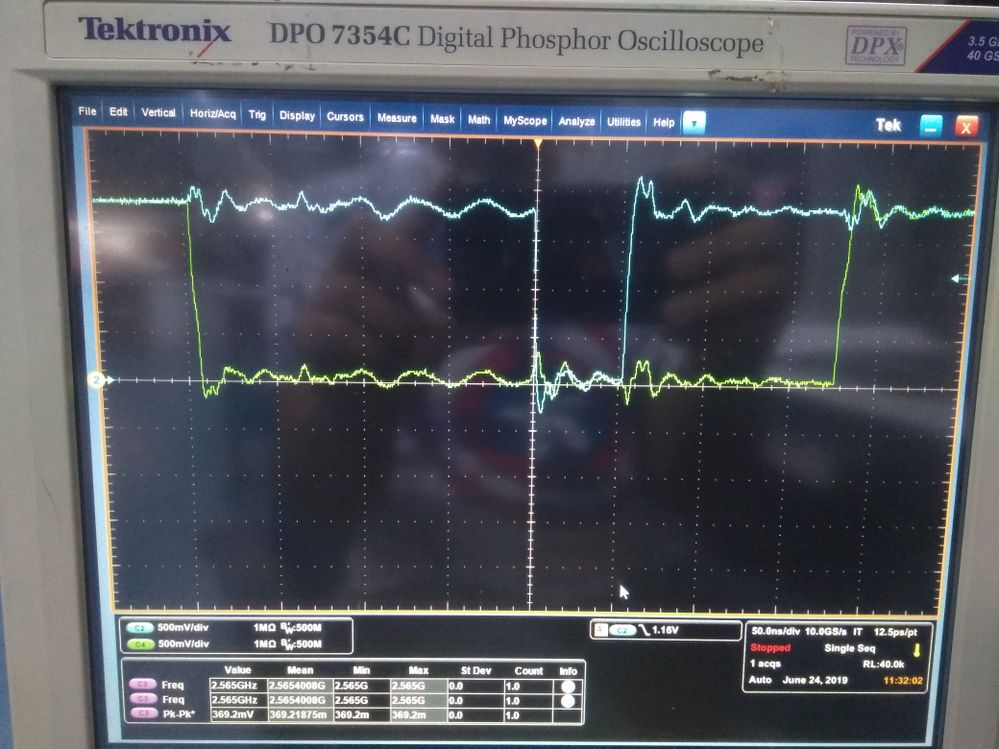

The waveform for CS and RDY_L is attached. The green waveform is for CS and the blue

waveform is for RDY_L. There are four IFC clock cycles between them (IFC running at 18MHz,

55ns clock cycle). The processor is also de-asserting CS indicating it has completed the

transaction before timeout.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please confirm that this is the trace for the failing read transaction.

What is the difference between traces of the transactions "md.w 0xffdf0000 1" and "md.w 0xffdf0050 1"?