- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

FXOS8700CQ is not generating Data ready interrupt on INT1

Hi,

I am using Hexiwear development kit. I have configured FXOS8700CQ to generate Data ready interrupt on INT1 (PTC1). But the INT1 interrupt never triggered. FXOS8700CQ configuration is mentioned below. Please let me know, am i missing some thing?

fxos_status_t FXOS_Init( handleFXOS_t* fxosHandle, const settingsFXOS_t* fxosSettings

)

{

/**

* initialize intern structures,

* which will be used from now on

*/

uint8_t chip_ID = 0x00;

uint8_t tmp[1] = {0};

memcpy( (void*)&self, (void*)fxosHandle, sizeof(self) );

memcpy( (void*)&settings, (void*)fxosSettings, sizeof(settings) );

statusI2C_t

status = I2C_Init( &(self.protocol), settings.address, settings.baudRate_kbps );

if ( STATUS_I2C_SUCCESS != status )

{

return status;

}

else

{

statusI2C_t

devStatus = STATUS_I2C_SUCCESS;

devStatus |= I2C_ReadReg( &(self.protocol), WHO_AM_I_REG, &chip_ID);

if(kFXOS_WHO_AM_I_Device_ID == chip_ID)

{

/** go to standby */

devStatus |= I2C_ReadReg(&(self.protocol), FXOS_CTRL_REG1, tmp);

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG1, tmp[0] & (uint8_t)~ACTIVE_MASK);

devStatus |= I2C_ReadReg(&(self.protocol), FXOS_CTRL_REG1, tmp);

if ((tmp[0] & ACTIVE_MASK) == ACTIVE_MASK)

{

catch( CATCH_I2C );

}

devStatus |= I2C_WriteReg(&(self.protocol), F_SETUP_REG, F_MODE_DISABLED); // Disable the FIFO

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG2, MOD_HIGH_RES); // /* enable auto-sleep, low power in sleep, high res in wake */

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_M_CTRL_REG1, (M_RST_MASK | M_OSR_MASK | M_HMS_MASK));

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_M_CTRL_REG2, (M_HYB_AUTOINC_MASK));

devStatus |= I2C_WriteReg(&(self.protocol), XYZ_DATA_CFG_REG, FULL_SCALE_4G); // +/-4g range with 0.244mg/LSB

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG4, 0x01); // Enable DRDY interrupt

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG5, INT_CFG_DRDY_MASK);

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG3, WAKE_FF_MT_MASK);

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG1, HYB_ASLP_RATE_0_8HZ | HYB_DATA_RATE_100HZ | ACTIVE_MASK);

devStatus |= I2C_ReadReg(&(self.protocol), FXOS_CTRL_REG1, tmp);

if ((tmp[0] & ACTIVE_MASK) != ACTIVE_MASK)

{

catch( CATCH_I2C );

}

if ( STATUS_I2C_SUCCESS != devStatus )

{

catch( CATCH_I2C );

}

}

return devStatus;

}

}

//Interrupt configuration

/** create basic tasks */

status |= HostInterface_Init();

SIM_SCGC5 |= SIM_SCGC5_PORTC_MASK; // Turn on clock to Port C module

PORTC_PCR1 |= (0|PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x1) |

PORT_PCR_IRQC(0xA)); // PC1 is configured for falling edge interrupts

//Enable PORTC interrupt on NVIC

NVIC_SetPriority( PORTC_IRQn, HEXIWEAR_TAP_IRQ_PRIO);

Thanks,

J. Chandra Sekhar

Hello Chandra,

I hope all is great with you. Thank you for using the NXP communities.

In this case, I highly recommend using the following bare metal project as a reference for your design:

FXOS8700CQ - Bare metal example project

I hope this information helps.

Regards,

David

Hi,

Thanks for your response.

I have checked the code and configured similarly in my Hexiwear board. But still the same, FXOS8700CQ sensor is not generating interrupt.

const gpio_input_pin_user_config_t Acc_cfg[] = {

{

.pinName = ACC_INT1,

.config.isPullEnable = false,

.config.pullSelect = kPortPullDown,

.config.isPassiveFilterEnabled = false,

.config.isDigitalFilterEnabled = false,

.config.interrupt = kPortIntDisabled

},

{

.pinName = ACC_INT2,

.config.isPullEnable = false,

.config.pullSelect = kPortPullDown,

.config.isPassiveFilterEnabled = false,

.config.isDigitalFilterEnabled = false,

.config.interrupt = kPortIntDisabled

},

{

.pinName = GPIO_PINS_OUT_OF_RANGE,

}

};

//Configured Pin 1 of PORTC as input

GPIO_DRV_Init( Acc_cfg, NULL );

//Sensor configuration

devStatus |= I2C_ReadReg( &(self.protocol), WHO_AM_I_REG, &chip_ID);

if(kFXOS_WHO_AM_I_Device_ID == chip_ID)

{

/** go to standby */

FXOS_GotoStandby();

devStatus |= I2C_ReadReg(&(self.protocol), FXOS_CTRL_REG1, tmp);

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG1, tmp[0] & (uint8_t)~ACTIVE_MASK);

devStatus |= I2C_ReadReg(&(self.protocol), FXOS_CTRL_REG1, tmp);

if ((tmp[0] & ACTIVE_MASK) == ACTIVE_MASK)

{

catch( CATCH_I2C );

}

devStatus |= I2C_WriteReg(&(self.protocol), XYZ_DATA_CFG_REG, FULL_SCALE_2G); // +/-2g range with 0.244mg/LSB

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_M_CTRL_REG1, (0x1F)); // Hybrid mode (accelerometer + magnetometer), max OSR

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_M_CTRL_REG2, 0x20); // M_OUT_X_MSB register 0x33 follows the OUT_Z_LSB register 0x06 (used for burst read)

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG2, 0x02); // High Resolution mode

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG3, 0x00); // Push-pull, active low

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG4, 0x01); // Enable DRDY interrupt

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG5, 0x01); // DRDY interrupt routed to INT1 - PTC1

devStatus |= I2C_WriteReg(&(self.protocol), FXOS_CTRL_REG1, 0x35); // ODR = 3.125Hz, Reduced noise, Active mode

FXOS_SetActive();

if ( STATUS_I2C_SUCCESS != devStatus )

{

catch( CATCH_I2C );

}

}

//Interrupt handler

void PORTC_IRQHandler(void)

{

PORT_HAL_ClearPortIntFlag(PORTC_BASE_PTR);

/** Write your code here ... */

/* Unblock the task by releasing the semaphore. */

portBASE_TYPE taskToWake = pdFALSE;

if (pdTRUE==xSemaphoreGiveFromISR(xReadRawDataSemaphore, &taskToWake))

{

FXOS8700CQ_DataReady = 1;

if (pdTRUE == taskToWake)

{

vPortYieldFromISR();

}

}

}

//Task to read data from sensor

void ReadRawData(task_param_t param)

{

xReadRawDataSemaphore = xSemaphoreCreateBinary();

if( xReadRawDataSemaphore == NULL )

{

configASSERT(0);

}

for(;;)

{

/*Block waiting for the semaphore to become available. */

if( xSemaphoreTake( xReadRawDataSemaphore, LONG_TIME ) == pdTRUE )

{

if(FXOS8700CQ_DataReady)

{

FXOS8700CQ_DataReady = 0;

FXOS_ReadRawData(&AccelMagData[0]);

}

vPortYieldFromISR();

}

}

}

Trying this from few days, but no luck. Request your support.

Thanks,

J. Chandra Sekhar

Hello Chandra,

Thank you for using the community.

Your device configuration seems correct. I just want to recommend applying a reset to all registers before device the configuration.

Could you please make sure the INT1 pin is connected to your MCU/MPU input pin? Is your input pin configured for falling edge interrupts?

Regards,

David

Hi,

To perform Soft reset, i have used below code. But this command resulting the STATUS_I2C_ERROR.

fxos_status_t FXOS_SoftReset()

{

statusI2C_t

i2cStatus = I2C_WriteReg( &(self.protocol), FXOS_CTRL_REG2, RST_MASK );

if ( STATUS_I2C_SUCCESS != i2cStatus )

{

return STATUS_FXOS_PROTOCOL_ERROR;

}

else

{

return STATUS_FXOS_SUCCESS;

}

}

Thanks,

J. Chandra Sekhar

Hello Chandra,

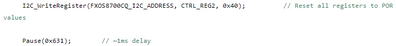

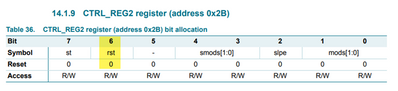

I do recommend performing the reset just writing 0x40 to the CTRL_REG2 register.

Could you please make sure the INT1 pin is connected to your MCU/MPU input pin? Is your input pin configured for falling edge interrupts?

Regards,

David