- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: s32k disabling the PLL

s32k disabling the PLL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Target is S32K144.

I'm trying to disable the SPLL,SOSC and FIRC clocks before entering VLPS mode

using the code snipt below will disable the last two but it fails to disable the SPLL.

Sorry it is a bit of mess.

2 different mask was used in the while loop:SPLLVLD bit which is commented out right now since I get stuck in it, The other one is LK bit that goes true but SPLLEN still remains 1.

SCG_RCCR = (uint32)((3 << 24)|(0 << 16)|(0 << 12)|(1 << 4)|(3 << 0));

SCG_SPLLCSR = (uint32)0x00; //&=~(1uL<<0);//(uint32)0x00; /* disable PLL */

while (SCG_SPLLCSR & 0x00800000UL /* 0x1000000*/){}; /* wait until PLL Lock is released */

SCG_SOSCCSR = (uint32)0x00; /* disable system OSC */

//SCG_RCCR = (uint32)((3 << 24)|(0 << 16)|(0 << 12)|(1 << 4)|(3 << 0));

SCG_FIRCCSR &= ~(1uL<<0); //disable FIRC

I NEED HELP RESOLVING THIS ISSUE.

Thanks,

Koorosh Hajiani

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

At first, "When entering VLPR/VLPS mode, the system clock should be SIRC"

void init_SIRC(void)

{

SCG->SIRCCSR &= ~ (1 << 24);

// [24] LK = 0 Unlock Control Status Register

SCG->SIRCCSR |= 0x01;

// [2] SIRCLPEN = 0 Slow IRC is disabled in VLP modes

// [1] SIRCSTEN = 0 Slow IRC is disabled in Stop modes

// [0] SIRCEN = 1 Slow IRC is enabled

SCG->SIRCDIV |= 0x0404;

// [10-8] SIRCDIV2 0b100 Divide by 8 (1MHz)

// [2-0] SIRCDIV1 0b100 Divide by 8 (1MHz)

while((SCG->SIRCCSR & (1 << 24)) == 0); // wait until clock is valid

// [24] SIRCVLD = 1 Slow IRC is enabled and output clock is valid

SCG->SIRCCSR |= (1 << 24);

// [24] LK = 1 lock Control Status Register

}

void switch_to_SIRC_in_RUN(void)

{

uint32_t srie = RCM->SRIE;

RCM->SRIE = 0x0000; // configure all reset sources to be ‘Reset' (not as Interrupt)

RCM->SRIE = 0xFFFF; // Program each reset source as Interrupt via RCM_SRIE

// for a minimum delay time of 10 LPO.

SCG->RCCR = 0x02010013;

// [27-24] SCS = 2 Slow IRC (SIRC_CLK 8MHZ)

// [19-16] DIVCORE = 1 Divide by 2 (4 MHz)

// [7-4] DIVBUS = 1 Divide core by 2 (2 MHz)

// [3-1] DIVSLOW = 3 Divide core by 4 (1 MHz)

while(!((SCG->CSR & (0x0F000000)) & 0x02000000));

// [27-24] SCS = 0b0010 Slow IRC (SIRC_CLK)

// or

while((SCG->SIRCCSR & (1 << 25)) == 0);

// [25] SIRCCSR = 1 Until SIRC is the system clock source

RCM->SRIE = srie;

}

Then disable FIRC, SOSC, and SPLL

void disable_FIRC_SIRC_SOSC_in_RUN(void)

{

// When entering VLPR/VLPS mode, the system clock should be SIRC. The FIRC, SOSC,

// and SPLL must be disabled by software in RUN mode before making any mode

// transition.

if(!(SCG->SPLLCSR & (1 << 25)))

{

SCG->SPLLCSR &= ~(1 << 0);

while(SCG->SPLLCSR & (1 << 24));

}

if(!(SCG->FIRCCSR & (1 << 25)))

{ // [25] FIRCSEL, if FIRC is not the system clock source

SCG->FIRCCSR &= ~(1 << 0);

// [0] FIRCEN = 0 FIRC disabled

while(SCG->FIRCCSR & (1 << 24));

// [24] FIRCVLD = 0 Fast IRC is not enabled or clock is not valid

}

if(!(SCG->SOSCCSR & (1 << 25)))

{

SCG->SOSCCSR &= ~(1 << 0);

while(SCG->SOSCCSR & (1 << 24));

}

}

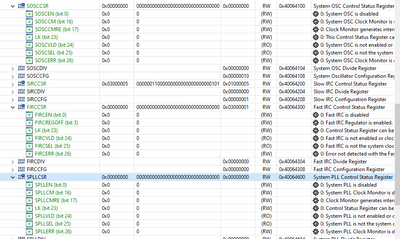

After that, all of them are disabled:

I hope it helps.

Best regads,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

At first, "When entering VLPR/VLPS mode, the system clock should be SIRC"

void init_SIRC(void)

{

SCG->SIRCCSR &= ~ (1 << 24);

// [24] LK = 0 Unlock Control Status Register

SCG->SIRCCSR |= 0x01;

// [2] SIRCLPEN = 0 Slow IRC is disabled in VLP modes

// [1] SIRCSTEN = 0 Slow IRC is disabled in Stop modes

// [0] SIRCEN = 1 Slow IRC is enabled

SCG->SIRCDIV |= 0x0404;

// [10-8] SIRCDIV2 0b100 Divide by 8 (1MHz)

// [2-0] SIRCDIV1 0b100 Divide by 8 (1MHz)

while((SCG->SIRCCSR & (1 << 24)) == 0); // wait until clock is valid

// [24] SIRCVLD = 1 Slow IRC is enabled and output clock is valid

SCG->SIRCCSR |= (1 << 24);

// [24] LK = 1 lock Control Status Register

}

void switch_to_SIRC_in_RUN(void)

{

uint32_t srie = RCM->SRIE;

RCM->SRIE = 0x0000; // configure all reset sources to be ‘Reset' (not as Interrupt)

RCM->SRIE = 0xFFFF; // Program each reset source as Interrupt via RCM_SRIE

// for a minimum delay time of 10 LPO.

SCG->RCCR = 0x02010013;

// [27-24] SCS = 2 Slow IRC (SIRC_CLK 8MHZ)

// [19-16] DIVCORE = 1 Divide by 2 (4 MHz)

// [7-4] DIVBUS = 1 Divide core by 2 (2 MHz)

// [3-1] DIVSLOW = 3 Divide core by 4 (1 MHz)

while(!((SCG->CSR & (0x0F000000)) & 0x02000000));

// [27-24] SCS = 0b0010 Slow IRC (SIRC_CLK)

// or

while((SCG->SIRCCSR & (1 << 25)) == 0);

// [25] SIRCCSR = 1 Until SIRC is the system clock source

RCM->SRIE = srie;

}

Then disable FIRC, SOSC, and SPLL

void disable_FIRC_SIRC_SOSC_in_RUN(void)

{

// When entering VLPR/VLPS mode, the system clock should be SIRC. The FIRC, SOSC,

// and SPLL must be disabled by software in RUN mode before making any mode

// transition.

if(!(SCG->SPLLCSR & (1 << 25)))

{

SCG->SPLLCSR &= ~(1 << 0);

while(SCG->SPLLCSR & (1 << 24));

}

if(!(SCG->FIRCCSR & (1 << 25)))

{ // [25] FIRCSEL, if FIRC is not the system clock source

SCG->FIRCCSR &= ~(1 << 0);

// [0] FIRCEN = 0 FIRC disabled

while(SCG->FIRCCSR & (1 << 24));

// [24] FIRCVLD = 0 Fast IRC is not enabled or clock is not valid

}

if(!(SCG->SOSCCSR & (1 << 25)))

{

SCG->SOSCCSR &= ~(1 << 0);

while(SCG->SOSCCSR & (1 << 24));

}

}

After that, all of them are disabled:

I hope it helps.

Best regads,

Diana