- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: VLPS to RUN delay

VLPS to RUN delay

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

VLPS to RUN delay

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We are meassuring a delay of over 500us from a wakeup event (falling edge in PORT) until the micro processes the related interrupt (PORT).

This seems to be too much.

We would like to get some support on this topic.

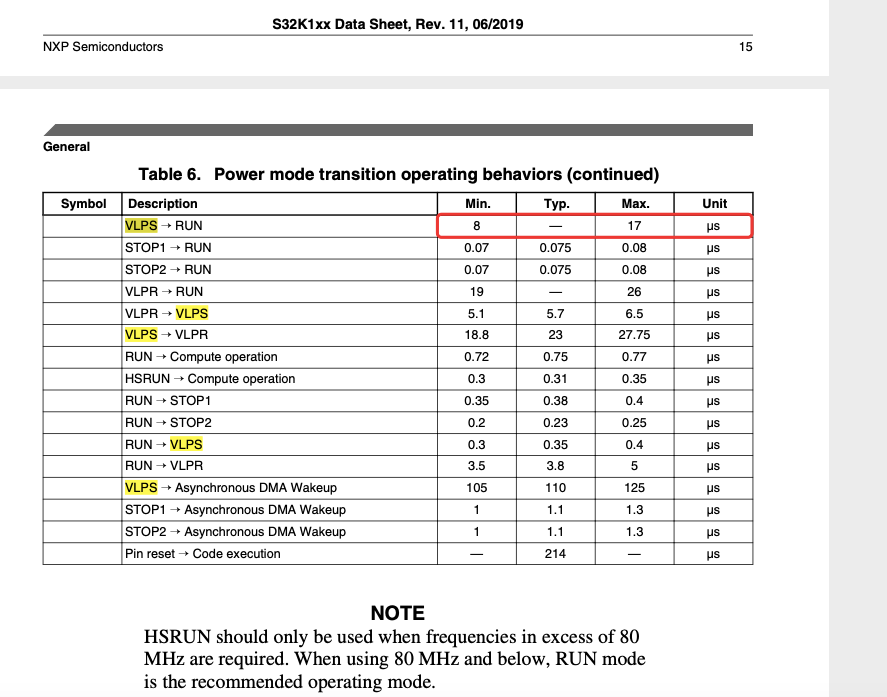

- Can we improve the wakeup reponse time?

- Is it specified somewhere the transition delay time from VLPS to RUN? In the past, I think I found a table with some numbers but I cannot find it anymore.

Thank you very much in advance.

Best regards,

Ricardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

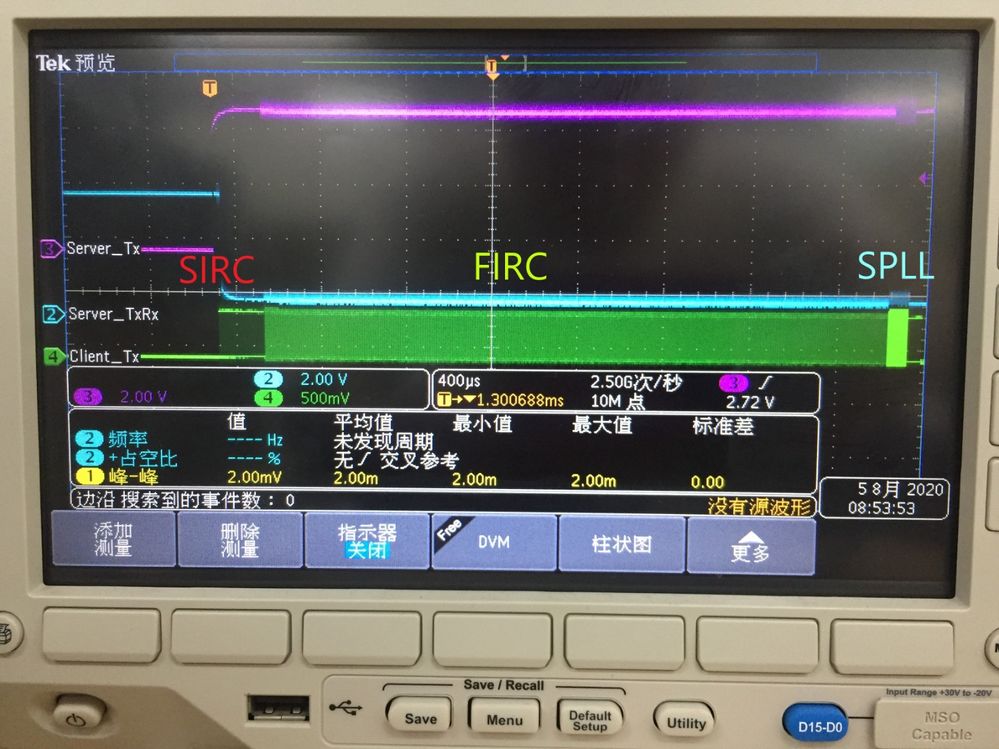

I can confirm that:

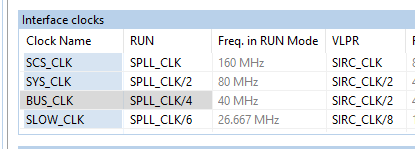

- When RUN mode clock is SPLL and when going to VLPS, then the wakeup time from VLPS to RUN is more than 500us.

- When RUN mode clock is FIRC, when going to VLPS, then the wakeup time from VLPS to RUN is around 10us, as stated in the datasheet.

So, it seems that waking up when the system clock is SPLL is much slower than with FIRC.

Could you please confirm our observations?

Why is this difference? Is this the time to lock the SPLL? Is this delay described in the datasheet or the RM?

Thank you.

Ricardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ricardo,

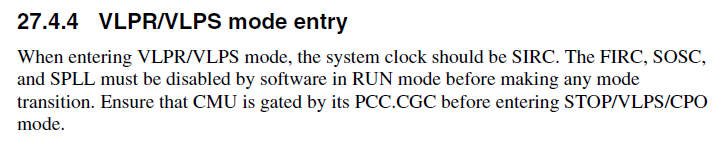

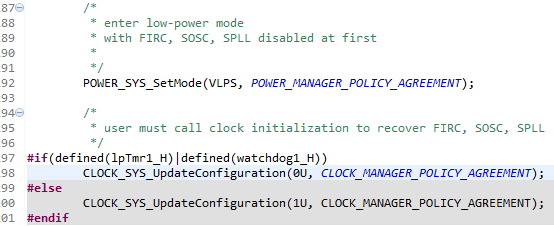

The system clock cannot be derived from FIRC/SPLL when the MCU enters VLPS.

The Power Manager SDK driver switches the clock to SIRC in the Power_SYS_Setmode(VLPS, ...) function.

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ricardo,

No matter you use SPLL or FIRC as the system clock, the time from VLPS to wakeup PORT ISR shouldn't be affected. The ISR will always be executed before the clock initializing.

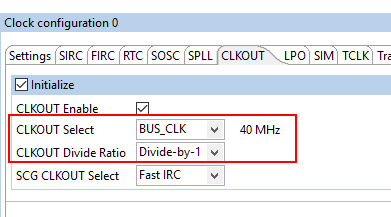

Also in the attached project, the system clock will switch to SPLL_CLK. And a clock out pin(PTE10) that connects to the bus clock is used to show the clock initialing procedure. You can test with the code directly.

Best wishes.

Jeremy

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ricardo, you can find the numbers in the datasheet as below.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy He,

Thanks for your response.

However, we are meassuring a delay of 500us from the PORT falling edge, which is the wakeup event, until the associated ISR is serviced.

What can be going on here? Maybe the system PLL is taking long to lock? Or what?

Any help or hint would be really appreciated. Because this makes no sense. Why the datasheet states max 17us but we can measure more than 500us.

Thank you

Ricardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ricardo,

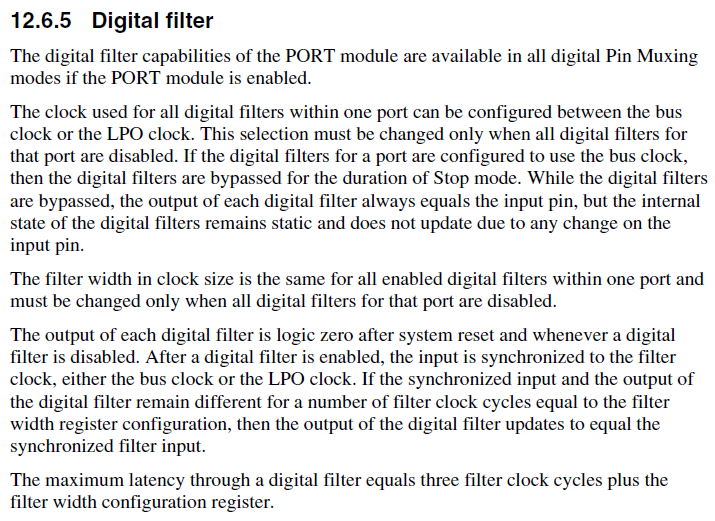

One possible reason could be a delay caused by Digital filter on that port.

Could you scope the active edge along with BUS_CLK on a CLKOUT pin?

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

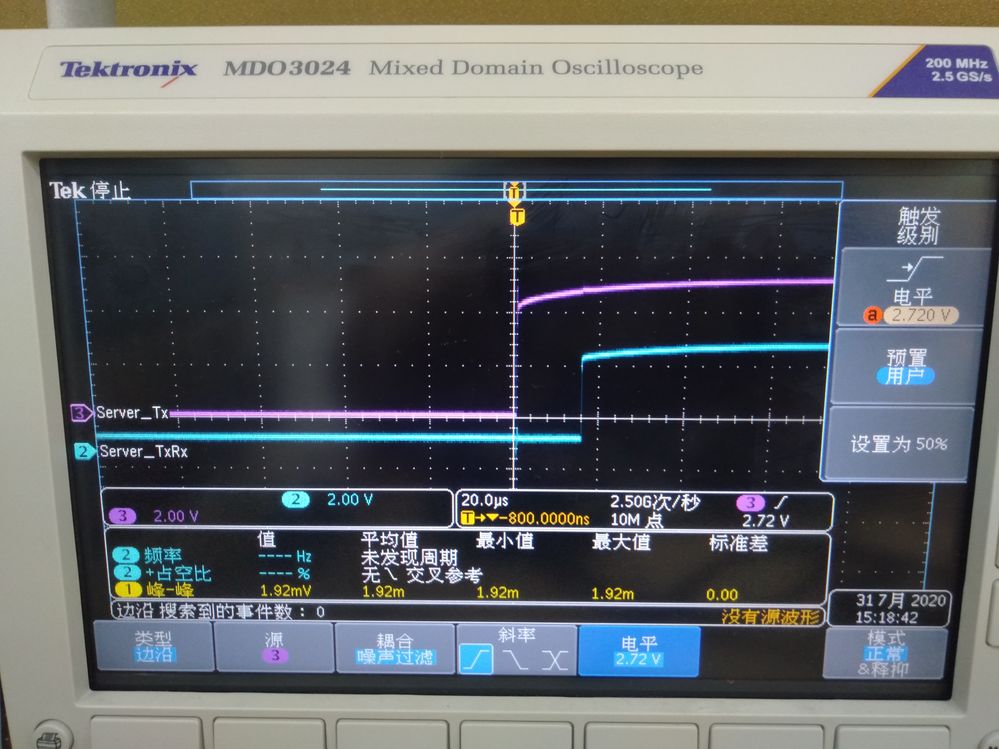

Hi Ricardo, I tested with a project using S32K144, The time from GPIO wake up to ISR toggle another pin is around 17 us, which matches the datasheet. Please check your code maybe something else is wrong.

On the below oscilloscope, Channel 3 is connected to the button SW2(PTC12), Channel 2 is connected to BLUE LED(PTD0) which toggled in PORT ISR after waking up from VLPS. Please check the attached project.