- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Use the S32K396 SDADC Error problem

Use the S32K396 SDADC Error problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Use the S32K396 SDADC Error problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi

我们在使用S32K396 SDADC转换做旋变测量,发现结果和实际相差较大,大约有100MV。该结果已经过偏置和增益增益标定,计算公式使用的是·(Vin/5V)*32767。使能DSP后误差变得更大,大约300mv。大家有遇到过类似的问题吗?该如何处理?

We used S32K396 SDADC conversion to measure the rotation, and found that the result was quite different from the actual one, about 100MV. The results have been calibrated for bias and gain gain using the formula ·(Vin/5V)*32767. After DSP is enabled, the error becomes larger, about 300mv. Have you ever had a similar problem? How to deal with it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you so much for your interest in our products and for using our community.

Please share your complete project in a zip, as we as HW (board connections) & SW (IDE and RTD versions) installation details in order to reproduce your issue from our side, like plug & play. Feel free to share any details to speed up the test and therefore the resolution of the problem.

Have a nice day!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks Leo. demo and sch as attached.

The development board I use is S32K396-LQFP-DC, and the filtering circuits of SDADC0 AN0 and AN1 channels are shown in the following figure.

I am testing the AN2 and AN3 channels of SDADC0, and the input circuit is shown below:

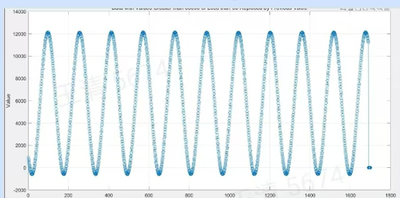

I use the FIFO interrupt of SDADC to transfer the collected data into the data array, and the FIR filter is not enabled in SDADC. I measured a 2V, 10kHz sinusoidal signal and the resulting data array is plotted in the following image.

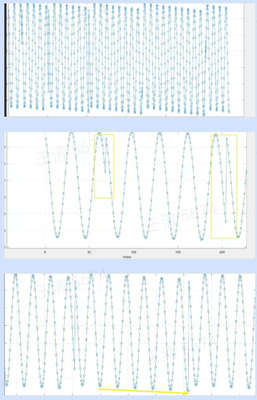

In this case, SDADC works fine; However, after the FIR filter is enabled, there are problems with the output data. The filtered converted data appears incomplete, with an abnormal downward shift in the signal, as shown in the figure below.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the details.

Seems the same issue that this thread:

The inconvenience is that you are using the S32K396-LQFP-DC, and we do not have access to said board, because it is not available in our NXP page, and therefore we cannot debug your issue on our side.

Please check if this issue is reproducible in the S32K396-BGA-DC1? And how?

If not, I'll need to ask you to contact your NXP representative or whoever provided you with the S32K396-LQFP-DC to follow up with your issue please. An apology for the inconvenience.

Have a nice day!