- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello all,

I'm using S32K146 device and I would like to use 16 ADC0 Channels to be sensed using PDB0 Triggering. Thus I provide the delays as follows. I'm using FTM so as to trigger the PDB Channels.

PDB0->CH[0].DLY[0] = 100;

PDB0->CH[0].DLY[1] = 200;

PDB0->CH[0].DLY[2] = 300;

PDB0->CH[0].DLY[3] = 340;

PDB0->CH[0].DLY[4] = 500;

PDB0->CH[0].DLY[5] = 600;

PDB0->CH[0].DLY[6] = 700;

PDB0->CH[0].DLY[7] = 800;

I need to raise an interrupt after 6 ADC sense (6th pre-trigger), but I'm getting a sequence error in this process.

I had the below questions.

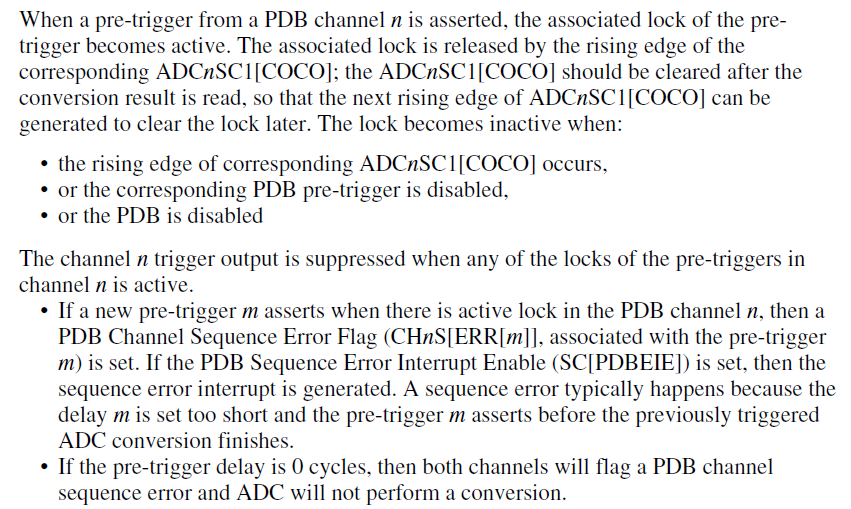

1. Do we need to read the ADC Channels (0-7) after every Conversion so as to enable to COCO Flag again? as it mentioned in RM below.

2. What is the minimum delay time between two pre-triggers?

Kindly help in this regard.

Thanks in advance,

Raju

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

1) yes, you need to read the result so the COCO will be cleared and thus can be set again which makes a pretrigger lock inactive.

2) delay time between two pre-triggers must be ADC conversion time at least.

See chapter 42.5.4.5 Sample time and total conversion time of the RM.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

1) yes, you need to read the result so the COCO will be cleared and thus can be set again which makes a pretrigger lock inactive.

2) delay time between two pre-triggers must be ADC conversion time at least.

See chapter 42.5.4.5 Sample time and total conversion time of the RM.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Petr,

Can you suggest any other alternative to reading the ADC values after every pre-trigger, since I need to convert the values & also implement certain functionalities which takes a sufficient amount of time?

There will be a high chance of another pre-trigger appears before the completion of the function.

Raju.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

you can try to use DMA to read a results, some examples are given here

Example S32K144 PDB ADC trigger DMA ISR S32DS

https://community.nxp.com/docs/DOC-343295

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Petr,

Thanks for the reply.

I tried accessing those

Example S32K144 PDB ADC trigger DMA ISR S32DS

the link was deleted I guess and below is the display it's showing.

Example S32K144 PDB ADC DMA S32DS.ARM.2018.R1

the zip file doesn't contain any data

Raju

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have uploaded the first one again, and see no issue with the second one.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Petr.

Thanks for your response.

I just downloaded Example S32K144 PDB ADC trigger DMA ISR S32DS and made suitable changes like clock and 42 (ADC0_COCO) DMAMUX source, everything works fine.

Now, I tried to add new TCD as I would like to use both ADC0 & ADC1. To make it simpler I just used only ADC1 not ADC0 with TCD[1] not TCD[0], so that later I can add both.

I just added a new function void DMA1_init(void) with all TCD[0] replaced with TCD[1] and new source & destination array. Also, I ensured the ADC1 with DMAEN.

Finally with void DMAMUX1_Init (void) --->

DMAMUX->CHCFG[1] |= DMAMUX_CHCFG_SOURCE(43);

Now my ISR is not executing. What changes I need to do so as to execute my isr ?

Kindly help in this regard.

Raju

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

not sure, are you able to share full example so this can be checked?

The SDK example I pointed last time is using both ADCs and DMAs are used to read them out, but probably you would like to have baremetal example.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

if the DMA ch1 is a source for interrupt in your modified code then correct interrupt init and interrupt vector have to be used. Try below code

void IRQs_Init (void)

{

FSL_NVIC->ICPR[0] = 1 << (1 % 32); /* IRQ1-DMA ch1: clr any pending IRQ*/

FSL_NVIC->ISER[0] = 1 << (1 % 32); /* RQ1-DMA ch1: enable IRQ */

FSL_NVIC->IP[1] = 0xA; /* IRQ1-DMA ch1: priority 10 of 0-15*/

}

void DMA1_IRQHandler(void)

{

PDB1->SC |= PDB_SC_SWTRIG_MASK; /* restart PDB counter */

DMA->CINT = 1; // clear DMA channel 1 interrupt flag

}

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Petr,

I had another question.

With back to back connection on all pdb channels but there is a trigger interrupt only for ADC_SC[8] still, there is a sequence error. But, will it affects other back to back triggers and its conversion as I would like to ignore the sequence error.

Kindly suggest the solution.

Raju

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

not sure of the overall configuration, but I assume that that the sequence error affects next back-to-back conversions on channel which indicate an error. And so you should resolve an error.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Petr,

Thanks for your feedback & it's really helpful.

As mentioned in the document, my calculation is as follows.

ADC TOTAL CONVERSION TIME = Sample Phase Time (set by SMPLTS + 1) + Hold Phase (1 ADC Cycle) + Compare Phase Time (8-bit Mode = 20 ADC Cycles, 10-bit Mode = 24 ADC Cycles, 12-bit Mode = 28 ADC Cycles) + Single or First continuous time adder (5 ADC cycles + 5 bus clock cycles)

i.e., for 12-bit conversion = (40+SMPLTS)/(fadc)

For our code SMPLTS=12. Therefore, conversion time = 53/40M =1.325us.

Considering that as conversion time if I keep PDB delay of 200 (200/80M=2.5us) between 0 & 1, I'm getting a sequence Error.

Am I correct in calculating the conversion time.

Kindly help in this regard.

Raju

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

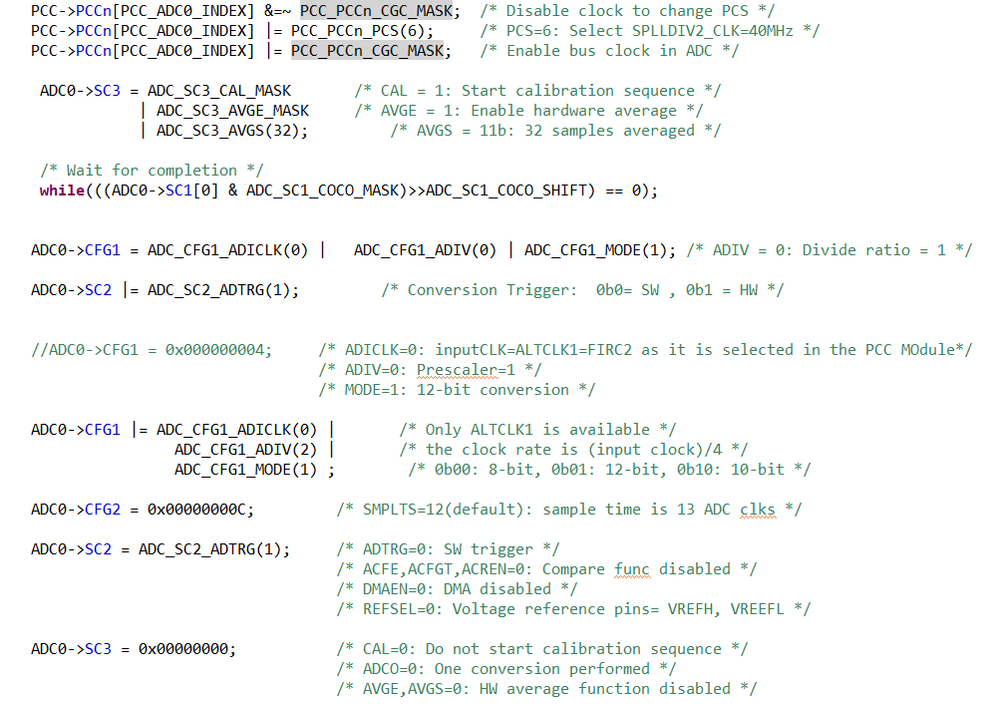

calculation looks correct. Do you really have ADCK 40MHz, what is the clock source?

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I tried changing the delay value where it works 450 counts it means, it takes 450/80M = 5.625us.

5.625 means with clock 40MHz it takes 225 ADC cycles to convert.

Kindly suggest where I went wrong.

ADC initialization as follows.

Raju

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

seems you have ADIV=2, so ADCK=10MHz

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Petr,

Thanks for the solution. Forgot to change the setting after initializing for calibration.

With 40MHz setting & with PDB Clock 80MHz it requires 104 counts between two delays. I tried keeping 110 it didn't work but it worked with 120 count.

Can I know any possible reasons?

Raju

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I guess there will be additional clocks due to triggering...

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Petr,

Thanks for your swift response.

I'm using PLLDIV2 which actually generates from 8MHZ External Oscillator & Below are my corresponding settings.

SCG->SPLLDIV = 0x00000302; /* SPLLDIV1 divide by 2; SPLLDIV2 divide by 4 */

PCC->PCCn[PCC_ADC0_INDEX] |= PCC_PCCn_PCS(6); /* PCS=6: Select SPLLDIV2_CLK=40MHz */

Raju

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

OK, so if you read result registers and the period of FTM is enough for all conversions, then it should work.

If have troubles still please share your full setting/code.

BR, Petr