- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K396 QSPI timeout

S32K396 QSPI timeout

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K396 QSPI timeout

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm trying to update my bare-metal S32K148 QSPI driver for the S32K396.

Clocks should be OK, MUX_0_DC_6 and MUX_10_DC_0 are enabled. LUTs are configured properly according to the new layout. MDAD/TGDAD are also configured, I can see that the IPCR register is written, the IP_ACC and BUSY bits are set in SR, and then... nothing happens! No other bits in SR/FR are set.

After quite some seconds the transaction times out. I can see the bits setting in FLSEQREQ.

The sequence I'm trying is only sending the command 0x9f on one line, reading back 8 bytes and then stop.Works on the S32K148. Did not check the signals with a scope yet.

What can be the issue that causes the timeout, what should I check? I believe, the code largely follows the flow of the "official" driver, but my hardware and the configuration can be slightly different.

Edit:

Measured with scope: signals are OK. Command goes out properly. As a test, added an address command to the LUT, that works too.

However, when I add a read command, SCK keeps running continuously, BUSY and IP_ACC remain set, and no TFF interrupt is generated. Any idea?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Thanks for looking into this issue. Please let me know what details could help with tracking down this issue.

The board is an NXP XS32K396-BGA-DC, the MCU mask set is 0P40E. We're using ARMGCC 10 and Trace32, not the NXP toolchain. All drivers are our bare-metal implementation, not using NXP drivers. It's a non-AUTOSAR (but automotive) project.

Clocks are configured as described in the reference manual, A+ for the S32K388. Do not have the S32K396 datasheet, that's another problem. Peripheral initialization and QSPI programming are performed as described in the manual and also following the flow in the NXP drivers.

The symptoms are still the same: command and address work, SPI signals are correct, and I get the TFF interrupt at the end. All good. But when I add a read command to the LUT, something breaks. The transfer never finishes, I can see SCK running forever, even when I stop execution with the debugger. Register contents are as described above, let me know what else could be interesting. Meanwhile SCK keeps running forever (or until the timeout - actually I haven't checked whether clock stops at the timeout).

I'm now double-checking all the clocks as from other messages here I have the feeling that QSPI might not work if the ratio of the clocks is not correct. Let me know what else can I check.

Best regards, Ferenc

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

At first I would recommend to download S32K396RM and DS. Both are available as secure file on the product webpage:

How to get secure access you may find out here:

https://www.nxp.com/support/support/secure-access-rights:SEC-ACCESS

You may use RTD drivers also under other environment than S32DS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Finally received the manual, datasheet and board schematics for S32K396. Unfortunately, I found nothing new that could be relevant for my issue. There are some bits in MCR that were missing from the docs of other derivatives, but no combination of settings worked for me so far.

Again, when the LUT is configured to send a QSPI command (1), address (2) and the write instruction (8), it works. If I add a read instruction (7) with either 1 or 4 pads, the BUSY and IP_ACC bits remain set indefinitely, the QSPI_SCK keeps running, and after some (quite long) time there is a timeout. The TFF flag is never set, there is no interrupt generated (timeout interrupt is not enabled for now). There is of course a stop instruction (0) too at the end of the LUT sequence.

The same driver works well on the S32K148 (of course adjusted for the different LUT layout etc...).

Since read is not working, is it possible that there is something wrong with DQS?

SOCCR=0x0e as recommended, QuadSPI_MCR_DQS_FA_SEL tested with all possible values, DQS_EN/DQS_OUT_EN all variations etc... Even configured the INTA pin and executed the pin toggling init sequence as described in the documentation to no avail. Btw I can't see that in the NXP driver. For clock init I'm using the code from the NXP example as it is. What can be wrong with my driver?

Best regards, Ferenc

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

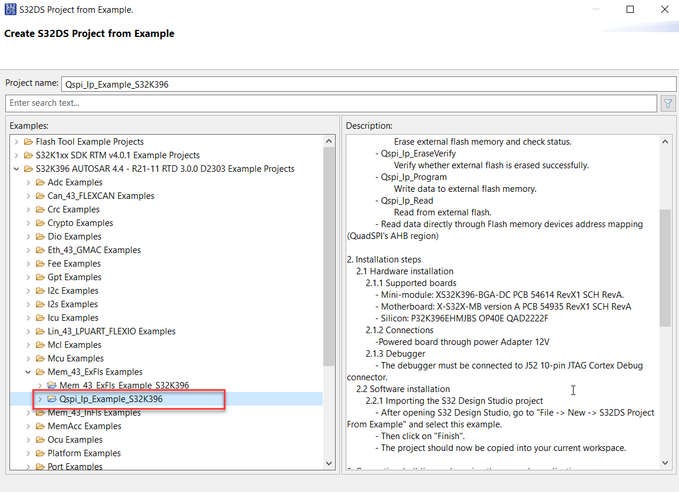

There is a new example for the device and QuadSPI, I believe it helps you to solve your issue.

Hope it helps

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you provide more details about your issue? Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Could you please suggest further debugging steps and describe what information could be helpful here? Spent a lot of time with experimenting but it simply does not work as expected.

Thanks, Ferenc

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Provided more details in my previous comment. Meanwhile switched to using the sys_init.c as it is from the examples, so clocking issues can now be excluded.

Symptoms are the same - nothing changed. When trying to read, the QSPI peripheral locks up. Any help would be appreciated.

Ferenc

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, did you find solution as i'm facing a similar issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @bert ,

I did not manage to resolve this issue and had to move to different projects meanwhile. I have no idea what's wrong. There is a chance that I'll revisit this project in the near future and give it another try. Should you find anything pls do let me know. I'll also post here.

Best regards, Ferenc