- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K358 - Linker script modification for M7_2

S32K358 - Linker script modification for M7_2

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K358 - Linker script modification for M7_2

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Everyone,

I’m currently working on the S32K358 board and aiming to run my application on Core 2. I have successfully compiled the code for Core 2, but I ran into a limitation with the .bss section size.

I initially modified the linker script to increase the size of the .bss section, and with the below changes it worked correctly.

However, I noticed that certain memory regions remain unused. To optimize memory usage, I tried further modifying the linker script to utilize these available regions.

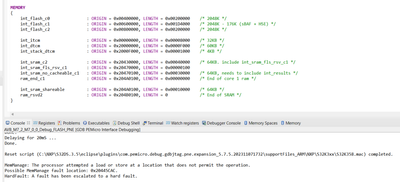

After below changes, the application builds successfully, but I encounter a hard fault at runtime.

Could anyone help me understand why this hard fault is occurring? Also, what is the correct and safe way to modify the linker script to effectively use the available memory for Core 2 without running into such faults?

Thanks in advance!

Best Regards,

Sathish.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I would recommend leaving all sections as they are, just moving their starting addresses and sizes as needed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From my analysis:

The *_c2 sections are not used in the M7_0 linker script.

The *_c0 sections are not used in the M7_2 linker script.

The *_c1 sections are not used in either M7_0 or M7_2 linker scripts.

I had removed these sections myself to keep only the memory regions relevant to each core in their respective linker scripts.

I’ve also verified the generated ELF file, and the section-to-memory mappings are correct.

Could you please clarify why you recommend leaving all sections as they are?

Additionally, the memory regions int_sram_c1, int_sram_fls_rsv_c1, int_sram_no_cacheable_c1 are currently unused in the linker script. I would like to utilize this memory for Core 2.

Could you please guide me on how this memory can be properly utilized by adjusting their starting addresses and sizes?

Thanks,

Sathish.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you attach whole your linker command file?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have uploaded the wrong screenshot for non-working case. Please find the right one here.

Regards,

Sathish.