- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Hello,

Currently, I am working on S32K312 SAF EVAL Package. I have a query related to NCF4 Fault injection.

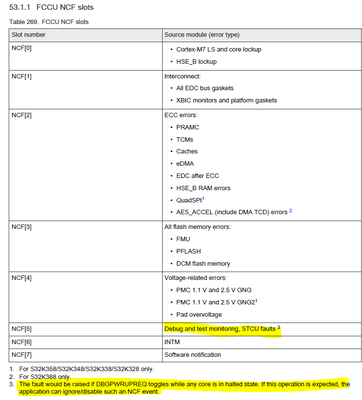

According to S32K3XXRM and S32K3_SAF_EMCEM_UM NCF4 is used for voltage related error.

I have query on below mentioned points.

1. Which EIM channel we should use for EIM fault injection in out of 31.

2. After successfully injection of error DCMROD4 register bit number 26 high for VDD1P1_GNG_ERROR?

3. Could you please provide application notes and demo example code for above mentioned error injection.

4. After injecting error using eMcem_InjectFault(EMCEM_DCM_NCF_4_INV_OUT1); this API returning E_OK. and FCCU Alarm is generated. but which register I need to read for confirmation of FCCU fault injected successfully?

Is NCF_S0 Register status is enough?

Aur apart of NCF_S0 register need to check status of DCM_GPR register like DCMRODn status?

Kindly provide me answer of above-mentioned points. I am looking forward for reply.

Thanks.

已解决! 转到解答。

- As you mention in previous reply.

[NXP] No it does not need to be checked as DCMRODn register remains 0x0 during injection. The injection is done only into NCF fault in FCCU.

But now while debugging observed after FCCU, NCF_5 fault injection DCMROD5 bit 9 and 11 is in high sate for all the NCF_5 fault injection which is available for S32K312. is it expected behavior? if yes, then why? please see the attachment.

[NXP] Yes you are right, I see the same in the tests. The NCF_5 has a special HW behavior. When injecting the NCF_5 faults there are also simultaneously other faults set by HW (EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF). Here is the table which faults are reported by eMcem alarm handler when injected:Fault injected: eMcem alarm handler for faults:

EMCEM_DCM_NCF_5_FAULT_MONITOR0 EMCEM_DCM_NCF_5_FAULT_MONITOR0, EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_FAULT_MONITOR1 EMCEM_DCM_NCF_5_FAULT_MONITOR1, EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_STCU_NCF EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_MBIST_BACKDOOR EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_MBIST_BACKDOOR, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_LMBIST_USER_CF EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_SYS_XFR_ERR EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF, EMCEM_DCM_NCF_5_SYS_XFR_ERR

EMCEM_DCM_NCF_5_DBG_ACTIVATION EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF, EMCEM_DCM_NCF_5_DBG_ACTIVATION

- Why for NCF_5 always above-mentioned bit of DCMROD5 is high, for all the DCM_NCF which is available for S32K312?

[NXP] NCF_5 has a specific HW behavior. - After Injection of NCF_5 observed STCU2, Register ERR_STAT bit 1 is always high for all the NCF_5 related FCCU fault injection? please see the attachment.

[NXP] Yes this bit is set as a result of NCF_5 injection. - What is the co-relationship between NCF_5 (FCCU) and STCU2 register ERR_STAT.? I tried to refer RM but unfortunately not able to understand (55.8.3). please see the attachment.

[NXP] As described in HW reference manual, NCF_5 includes faults for STCU2 so the bit in STCU is set as part of fault injection. - After injection of error using eMcem_InjectFault(EMCEM_DCM_NCF_5_FAULT_MONITOR0); API, it is returning E_OK, Also FCCU ALARM is generated and NCF_S0 bit 5 is in high state. so, I am assuming FCCU fault is injected successfully. is my understanding correct? please see the attachment.

[NXP] Yes your understanding is correct. - Is NCF_5 available for STCU fault injection?

[NXP] You can call this API:

retStatus = eMcem_InjectFault(EMCEM_DCM_NCF_5_STCU_NCF); - If above mentioned point is correct then how we can inject NCF_5 fault of debug and test monitoring.?

[NXP] You can call this API:

retStatus = eMcem_InjectFault(EMCEM_DCM_NCF_5_DBG_ACTIVATION);

retStatus = eMcem_InjectFault(EMCEM_DCM_NCF_5_FAULT_MONITOR0);

retStatus = eMcem_InjectFault(EMCEM_DCM_NCF_5_FAULT_MONITOR1);

Best Regards,

Frantisek

Hello,

here are the answers:

1. Which EIM channel we should use for EIM fault injection in out of 31.

[NXP] There is no EIM that would allow to inject voltage related errors. The list of supported EIMs is described in HW reference manual (S32K3xxRM_Rev7.pdf, section 51.1.2 EIM channel mapping).

2. After successfully injection of error DCMROD4 register bit number 26 high for VDD1P1_GNG_ERROR?

[NXP] After injecting the fault the NCFS4 bit in FCCU status register (NCF_S0) is set (no bits are set in DCMRODn registers).

3. Could you please provide application notes and demo example code for above mentioned error injection.

[NXP] The example for FCCU fault injection is provided in SAF example application in main.c file

c:\NXP\S32K3_SAF_1.0.3_EVAL\S32_SAF_Demo\src\main.c

where there is example how to inject fault by calling this API:

eMcem_InjectFault( EMCEM_DCM_NCF_1_AD_EDC_ERR_OUT );

This example injects EMCEM_DCM_NCF_1_AD_EDC_ERR_OUT fault. To inject EMCEM_DCM_NCF_4_INV_OUT1 it is only needed to pass EMCEM_DCM_NCF_4_INV_OUT1 parameter as follows:

retStatus = eMcem_InjectFault(EMCEM_DCM_NCF_4_INV_OUT1);

4. After injecting error using eMcem_InjectFault(EMCEM_DCM_NCF_4_INV_OUT1); this API returning E_OK. and FCCU Alarm is generated. but which register I need to read for confirmation of FCCU fault injected successfully?

[NXP] This is the expected behaviour, i.e. API returning E_OK and FCCU alarm notification called.

Is NCF_S0 Register status is enough?

[NXP] Yes.

Aur apart of NCF_S0 register need to check status of DCM_GPR register like DCMRODn status?

[NXP] No it does not need to be checked as DCMRODn register remains 0x0 during injection. The injection is done only into NCF fault in FCCU.

Best Regards,

Frantisek

Hello @frantisekdobes ,

Thanks for your quick reply,

Now my previous query got resolved after your reply.

After further debugging on FCCU I have another query.

1. As you mention in previous reply.

[NXP] No it does not need to be checked as DCMRODn register remains 0x0 during injection. The injection is done only into NCF fault in FCCU.

But now while debugging observed after FCCU, NCF_5 fault injection DCMROD5 bit 9 and 11 is in high sate for all the NCF_5 fault injection which is available for S32K312. is it expected behavior? if yes, then why? please see the attachment.

2. Why for NCF_5 always above-mentioned bit of DCMROD5 is high, for all the DCM_NCF which is available for S32K312?

3. After Injection of NCF_5 observed STCU2, Register ERR_STAT bit 1 is always high for all the NCF_5 related FCCU fault injection? please see the attachment.

4. What is the co-relationship between NCF_5 (FCCU) and STCU2 register ERR_STAT.? I tried to refer RM but unfortunately not able to understand (55.8.3). please see the attachment.

5. After injection of error using eMcem_InjectFault(EMCEM_DCM_NCF_5_FAULT_MONITOR0); API, it is returning E_OK, Also FCCU ALARM is generated and NCF_S0 bit 5 is in high state. so, I am assuming FCCU fault is injected successfully. is my understanding correct? please see the attachment.

6. Is NCF_5 available for STCU fault injection?

7. If above mentioned point is correct then how we can inject NCF_5 fault of debug and test monitoring.?

I am looking forward for your reply.

Thanks

- As you mention in previous reply.

[NXP] No it does not need to be checked as DCMRODn register remains 0x0 during injection. The injection is done only into NCF fault in FCCU.

But now while debugging observed after FCCU, NCF_5 fault injection DCMROD5 bit 9 and 11 is in high sate for all the NCF_5 fault injection which is available for S32K312. is it expected behavior? if yes, then why? please see the attachment.

[NXP] Yes you are right, I see the same in the tests. The NCF_5 has a special HW behavior. When injecting the NCF_5 faults there are also simultaneously other faults set by HW (EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF). Here is the table which faults are reported by eMcem alarm handler when injected:Fault injected: eMcem alarm handler for faults:

EMCEM_DCM_NCF_5_FAULT_MONITOR0 EMCEM_DCM_NCF_5_FAULT_MONITOR0, EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_FAULT_MONITOR1 EMCEM_DCM_NCF_5_FAULT_MONITOR1, EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_STCU_NCF EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_MBIST_BACKDOOR EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_MBIST_BACKDOOR, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_LMBIST_USER_CF EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF

EMCEM_DCM_NCF_5_SYS_XFR_ERR EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF, EMCEM_DCM_NCF_5_SYS_XFR_ERR

EMCEM_DCM_NCF_5_DBG_ACTIVATION EMCEM_DCM_NCF_5_STCU_NCF, EMCEM_DCM_NCF_5_LMBIST_USER_CF, EMCEM_DCM_NCF_5_DBG_ACTIVATION

- Why for NCF_5 always above-mentioned bit of DCMROD5 is high, for all the DCM_NCF which is available for S32K312?

[NXP] NCF_5 has a specific HW behavior. - After Injection of NCF_5 observed STCU2, Register ERR_STAT bit 1 is always high for all the NCF_5 related FCCU fault injection? please see the attachment.

[NXP] Yes this bit is set as a result of NCF_5 injection. - What is the co-relationship between NCF_5 (FCCU) and STCU2 register ERR_STAT.? I tried to refer RM but unfortunately not able to understand (55.8.3). please see the attachment.

[NXP] As described in HW reference manual, NCF_5 includes faults for STCU2 so the bit in STCU is set as part of fault injection. - After injection of error using eMcem_InjectFault(EMCEM_DCM_NCF_5_FAULT_MONITOR0); API, it is returning E_OK, Also FCCU ALARM is generated and NCF_S0 bit 5 is in high state. so, I am assuming FCCU fault is injected successfully. is my understanding correct? please see the attachment.

[NXP] Yes your understanding is correct. - Is NCF_5 available for STCU fault injection?

[NXP] You can call this API:

retStatus = eMcem_InjectFault(EMCEM_DCM_NCF_5_STCU_NCF); - If above mentioned point is correct then how we can inject NCF_5 fault of debug and test monitoring.?

[NXP] You can call this API:

retStatus = eMcem_InjectFault(EMCEM_DCM_NCF_5_DBG_ACTIVATION);

retStatus = eMcem_InjectFault(EMCEM_DCM_NCF_5_FAULT_MONITOR0);

retStatus = eMcem_InjectFault(EMCEM_DCM_NCF_5_FAULT_MONITOR1);

Best Regards,

Frantisek