- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K144 UART FIFO Example

S32K144 UART FIFO Example

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K144 UART FIFO Example

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

Is anyone used UART FIFO for S32K144?

LPUART2->CTRL &= (0xC0000); // Disable TE and RE for Setting FIFO

LPUART2->FIFO |= 0x000000ff; // Enable TX and RX FIFO for 256 bytes

LPUART2->CTRL |= (0xC0000); // Enable TE and RE after for Setting FIFO

After this also am receiving only 4 bytes and RX OverFlow is set.

Please let me know if anyone has done these experiments.

Thanks in Advance..!

Harish G

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

Thanks for the response. Please release errata sheet, your user manual gives a different impression. However, if it's not possible to use FIFO, I'm okay to use DMA. But I have another question LPUART MATCH can trigger interrupt asper the user manual. we found it's not working either. please confirm.

LPUART0->MATCH = 0x00320031; // Match1: '1' and Match2: '2'

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harish,

I understand that it can be confusing, however, the RM is correct:

Regarding your second question:

The CTRL[MA2IE] actually enable MA2F interrupt. If MA2F is not set the interrupt is not generated.

The section 51.4.4.2.6 Match On Match Off operation describes that " The character that matches

MATCH[MA2] and all following characters are discarded". That is mean the character that matches

MATCH[MA2] is not placed to receive data buffer. If the character is not moved into receive data buffer the MA2F is not set and the interrupt does not occur.

You can try a simple test where BAUD[MAEN2] = 0. After that, the character which matches MA2 is moved to the receive data buffer and the MA2F is set, but the following data will be also moved into the receive data buffer (the data won't be discarded as is described in the "Match On and Match Off" section).

I hope it helps.

Best Regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Diana,

Thank you for the detailed info. We will do some experiment on this and get back to you.

I have few doubts on HW Flow Control for UART in S32K144.

We are configuring MODIR register to 0x9 // TXCTSE bit 1 and RXRTSE=1 and later we are not receiving any data from the modem, we don't know that transmitted data received by modem or not also.

And we wanted to know that what are bits to be configured for Full Modem support in MODIR register (RTS and CTS lines are interconnected b/w microcontroller and modem).

Please let us know what are bits to be configured in MODIR register so that RX Overrun Interrupt should not occur even if don't read DATA register for some time.

Regards,

Harish G

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harish,

I'm very sorry for the delay.

If you have an RX overrun let's check first your LPUART settings. What is your baudrate, clock settings?

Regarding hardware flow control, could you please share the screen from oscilloscope/analyzer where can be seen the RTS, CTS, Rx, Tx?

Thank you in advance.

Best Regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harish,

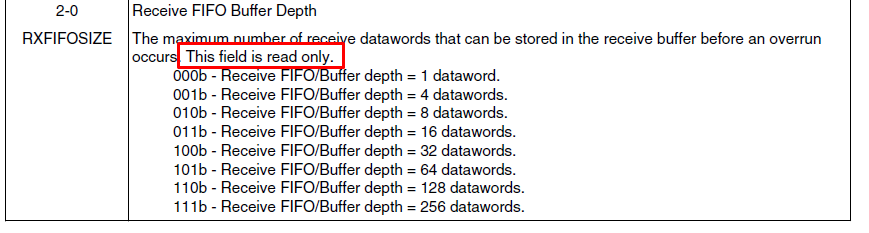

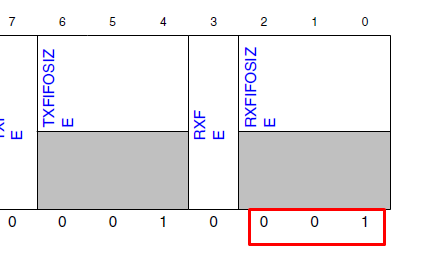

Unfortunately, the TXFIFOSIZE and RXFIFOSIZE fields are read-only, the Buffer depth is only 4 datawords for the S32Kxx devices.

Best Regards,

Diana