- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I'm planning to implement a boot loader on the S32K144EVB which is going to be used as basis for the production bootldr.

I'm planning to start my boot loader at location 0 and the APP at the 1ST 64Kbyte boundary. which will be accomplished by writing the offset in the VTOR register and then jump to 0x10004 after the APP image has been flashed.

My QUESTION IS:

Can I issue the ERASE and PROGRAM command from the boot loader residing in the flash section starting at 0x00 to 0xffff targeting the application locations(0x10000-- whatever)?

If the answers is yes then what are the sections of the flash that this could be done?

and what is the following paragraph actually stating(page 714 ref man)?

While executing from a particular PFLASH read partition , FTFC commands (except

parallel boot) cannot run over that PFLASH read partition.

Knowing that s32k144 has only one partition of 512k.

Now is parallel boot is a normal boot the one that takes place every time the board is powered up?

This a bit confusing,

Thanks,

Koorosh Hajiani

248-778-6396

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I just talked with S32DS expert to be sure... You can use pre-defined .code_ram section. Startup files then contains this piece of code which copies the code to RAM (it's in startup.c):

/* Copy functions from ROM to RAM */

while (code_rom_end != code_rom)

{

*code_ram = *code_rom;

code_ram++;

code_rom++;

}

If you use own section (not .code_ram), you must copy the code by yourself (for example by memcpy) or you must re-write the startup code, so it copies also your new section.

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Many thanks for your answer.

so, basically just do this:

__attribute__ ((section(".code_ram"))) // place the code below into .code_ram section

void EraseAndProgram(void);

is that correct?

Also something unrelated to this.

If my Program flash size is say 1M or 2M then according to the reference manual there are more than 1 bank in the flash and if I'm not mistaken I can run ERASE/PROGRAM command from bank1 to modify bank2.

Is that correct?

Thanks,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

you can't erase/program PFLASH when the code is running from PFLASH. Take a look at:

I shared simple example here:

Example S32K144 Flash RW simple

It shows how to force some code to RAM memory.

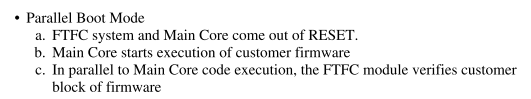

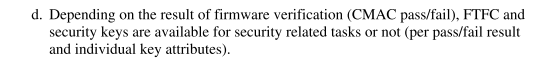

Parallel boot mode is kind of secure boot:

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Lukas,

Thanks for your reply, It contains very useful information. I also looked the project you provided which is also very helpful.

Just a few questions to make sure I understand every thing.

In main.c you have:

__attribute__ ((section(".MyRamCode"))) // place the code below into .MyRamCode section

This will place this function at the load address of "MyRamCode" section which is at "m_my_flash" section which is at

0x0007FE00 according to the linker file, and then use memcpy to move it to RAM at m_my_ram(0x20006E00).

which is fine.

I was wondering however if we could use the attribute to place this function in the .data section so that the start up code do the copying,

Is there a reason not to do that?

I have a few more questions on RWW part of the flash that will ask later.

Thanks,

Koorosh Hajiani

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I just talked with S32DS expert to be sure... You can use pre-defined .code_ram section. Startup files then contains this piece of code which copies the code to RAM (it's in startup.c):

/* Copy functions from ROM to RAM */

while (code_rom_end != code_rom)

{

*code_ram = *code_rom;

code_ram++;

code_rom++;

}

If you use own section (not .code_ram), you must copy the code by yourself (for example by memcpy) or you must re-write the startup code, so it copies also your new section.

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for all, this topic helps me a lot.

In spite of that, i have always some problems :

I try to access to the flash with indications that you describe above.

I place the code in .code_ram section, (I work with the SDK version 1.0 and S32DS 2.0).

But when i send instructions to the FTFC, the board reset.

More surprising, the process works if i execute the code step by step in debug mode.

Indeed i need to place a breakpoint on the last 'while instruction' for each sequence.

If i try to execute this last while, without breakpoint, the board restart.

In second time, I try to use the CSEC module to generate a random number and i have some problems.

The CSEC module works on the S32K144-Q100 board but doesn't work on the FRDMDK-144-Q100 board.

The difference between these two boards seems to be the chip reference.

The S32K144-Q100 has the PS32K144UAVLL and the FRDMPK144-Q100 has the PS32K144HFVLL.

I don't know why the freescale version doesn't work.

Furthermore, the SDK if define only for the PS32K144HFVLL version and not for PS32K144UAVLL.

So, to compile on the NXP board, we define the MCU as PS32K144HFVLL but that works, so i continue like this.

Can you confirm that the SDK works the same for these two references?

Thanks,

Alexandre HOCHART.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Alexandre,

I am facing the same issue of board getting reset as you mentioned above when executing FTFC.

As you mentioned it works when putting breakpoints but doesn't without a breakpoint.

Can you share how you were able to solve this issue?

Thanks & Regards,

Vikas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Vikas,

I'm apologize i can't remember how i solved it.

But i can give you my FTFC command function.

I also remember something about HSRUN clock mode limitation with the FTFC module.

Initialization:

FLASH_DRV_Init(&flash1_InitConfig0, &internalFlash_flashSSDConfig);

if (internalFlash_flashSSDConfig.EEESize == 0) {

FLASH_DRV_DEFlashPartition(&internalFlash_flashSSDConfig, 0x2, 0x4, 0x3, true, true);

}

CSEC_DRV_Init(&csec1_State);

CSEC_DRV_InitRNG();

Prototype:

void executeFlashCommand(uint8_t a_cmd, uint32_t a_addr, uint8_t *a_pageBuffer) __attribute__ ((section(".code_ram")));

Function:

void executeFlashCommand(uint8_t a_cmd, uint32_t a_addr, uint8_t *a_pageBuffer) {

uint8_t v_AddrVec[3];

v_AddrVec[0] = (a_addr & 0x00FF0000) >> 16;

v_AddrVec[1] = (a_addr & 0x0000FF00) >> 8;

v_AddrVec[2] = (a_addr & 0x000000FF) >> 0;

INT_SYS_DisableIRQGlobal();

while ((FTFC->FSTAT & FTFC_FSTAT_CCIF_MASK) == 0);

FTFC->FSTAT = FTFC_FSTAT_ACCERR_MASK | FTFC_FSTAT_FPVIOL_MASK;

FTFC->FCCOB[3] = a_cmd; //Program Phrase command (0x07)

FTFC->FCCOB[2] = v_AddrVec[0]; //Flash address [23:16]

FTFC->FCCOB[1] = v_AddrVec[1]; //Flash address [15:08]

FTFC->FCCOB[0] = v_AddrVec[2]; //Flash address [7:0]

if (a_pageBuffer != NULL) {

FTFC->FCCOB[7] = a_pageBuffer[0]; //data

FTFC->FCCOB[6] = a_pageBuffer[1];

FTFC->FCCOB[5] = a_pageBuffer[2];

FTFC->FCCOB[4] = a_pageBuffer[3];

FTFC->FCCOB[11] = a_pageBuffer[4];

FTFC->FCCOB[10] = a_pageBuffer[5];

FTFC->FCCOB[9] = a_pageBuffer[6];

FTFC->FCCOB[8] = a_pageBuffer[7];

}

FTFC->FSTAT = FTFC_FSTAT_CCIF_MASK; //launch command

while ((FTFC->FSTAT & FTFC_FSTAT_CCIF_MASK) == 0); //wait for done

INT_SYS_EnableIRQGlobal();

}