- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

S32K144 CAN 2.0 sample code

Hello all,

I am using S32K144 eval board.

I want to create a workspace for normal can communication with baud rate as 500kbps.

I need sample code for CAN 2.0 for s32k144 ,if any application note is there for can 2.0 in s32k144 also share that too.

Any leads are appreciated.

Thanks.

Hi,

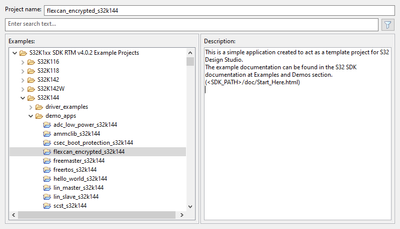

you can refer to demo examples in S32DS 2.2

This example follows https://www.nxp.com/docs/en/application-note/AN5413.pdf code, see chapter 2.9.

There is also SDK based demo

Similar SDK example is also in S32DS3.4

BR, Petr

Thanks! peter for the prompt response.

I have imported the project but it seems the code has the CAN FD feature enabled what to do to disable it completely from the code such that it can work for normal CAN 2.0 communication with payload 8byte.

Thanks.

Hi,

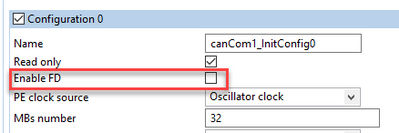

CAN FD is disabled by clearing MCR[FDEN] bit. In SDK it is done by unchecking "Enable FD" option in flexcan component.

Anyway , even if CAN FD is enabled. FlexCAN is able to receive and transmit messages in both CAN FD and CAN 2.0 formats.

BR, Petr

Hi PeterS,

Thanks for the response.

I am using s32k144 with 20 MHz crystal.

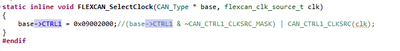

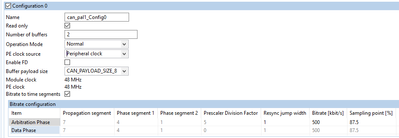

I wanted to know can bit time setting for 500KHz , and ctrl setting as per below snap for the same sample code,sys clk selected is 80Mhz

so what should i set for below register in the sample code such that the can communication can take place for 8Mhz Sclock (derived from above CTRL1 register setting) and 500KHz bitrate for Can communication.

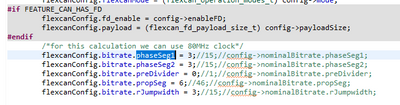

In canpal flexcan sample code , i have done below changes , .enablefd=false, .length = 8, payload selected as 8byte and disabled the FEATURE_CAN_HAS_FD macro in the code.

Please let me know if any other register value needs to be updated for standard CAN changes and also confirm the CAN bite setting for register phaseSeg1, phaseSeg2,predivider,propSeg and rJumpwidth.

Thanks.

Hi,

if using SDK do not modify driver code, rather do a setting in PE components

You can disable CAN FD, select PE clock source, and change desired Bitrate and sampling point. Bit timing segment will be calculated.

BR, Petr