- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K144 BusFault while checking CCIF after launching Partition FlexNVM

S32K144 BusFault while checking CCIF after launching Partition FlexNVM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was hoping someone could help me shed light on an issue I'm having.

The problematic code

uint32_t eeIsFlexNvmPartitioned(void)

{

/*

"DEPART field contains 0xF for non-partitioned devices."

*/

return ((SIM->FCFG1 & SIM_FCFG1_DEPART_MASK) != SIM_FCFG1_DEPART_MASK);

}

void eePartitionFlexNvm(void)

{

while ((FTFC->FSTAT & FTFC_FSTAT_CCIF_MASK) != FTFC_FSTAT_CCIF_MASK)

{

/* Wait for command execution to finish. */

}

/*

See S32K-RM 36.5.9.1.3 Command execution and error reporting.

*/

if (FTFC->FSTAT & (FTFC_FSTAT_ACCERR_MASK | FTFC_FSTAT_FPVIOL_MASK))

{

FTFC->FSTAT |= FTFC_FSTAT_ACCERR_MASK | FTFC_FSTAT_FPVIOL_MASK;

}

/*

See AN11983 and S32K-RM 36.4.4.1.6.1

*/

FTFC->FCCOB[3] = 0x80; /* FCCOB0: Selects the PGMPART command */

FTFC->FCCOB[2] = 0x00; /* FCCOB1: No CSEc operation */

FTFC->FCCOB[1] = 0x00; /* FCCOB2: No CSEc operation */

FTFC->FCCOB[0] = 0x00; /* FCCOB3: FlexRAM loaded with valid EEPROM during reset sequence */

FTFC->FCCOB[7] = 0x02; /* FCCOB4: EEPROM data set size code: EEESIZE = 2 (4 kB) */

FTFC->FCCOB[6] = 0x03; /* FCCOB5: FlexNVM Partition code: DEPART = 3 (Data flash: 32 kB, EEPROM backup: 32 kB) */

/*

Execute command.

*/

FTFC->FSTAT |= FTFC_FSTAT_CCIF_MASK;

/*

This line causes a busfault.

*/

while ((FTFC->FSTAT & FTFC_FSTAT_CCIF_MASK) != FTFC_FSTAT_CCIF_MASK)

{

/* Wait for command execution to finish. */

}

}

Application code only calls eePartitionFlexNvm when eeIsFlexNvmPartitioned returns 0. The code is run from bank 0 P-flash. I am operating under the assumption that programming/partitioning bank 1 from bank 0 is OK.

The problem

When the application is run, the last line of code in eePartitionFlexNvm causes the following fault:

BusFault: A bus fault has occurred during instruction prefetching.

This also seems to occur when not debugging. For some reason, debugging and using step-by-step debugging seems to work well.

Other remarks

- I have tried setting OCM1 in OCMDR0 and OCMDR1 to 0x3 before the command execution to no avail.

- Executing the code from RAM seems to solve the issue, but I was under the impression this would not be necessary, and feels like a work-around rather than a proper fix.

Questions

- What is the mechanism behind this fault? I thought programming FlexNVM/D-flash from P-flash should not be a problem.

- I saw a similar problem on StackOverflow where the OT suggested "Disabling caching by writing LMEM->PCCRMR = 0;" solved their problem. Is this a valid solution? I haven't specifically enabled caching. I also do not see anything mentioned about this in AN11983 or the sample project flash_partitioning_s32k144.

- How can I solve this problem?

Kind regards,

Joey

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joey,

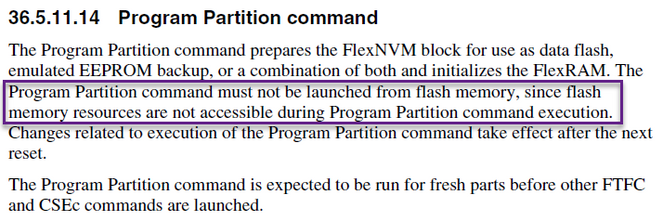

The command must be launched from SRAM or through JTAG/SWD.

A function can be placed in SRAM as it is shown here:

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joey,

The command must be launched from SRAM or through JTAG/SWD.

A function can be placed in SRAM as it is shown here:

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

i tried this solution but still problem exist.

Do i need to enable the IRQ also?

without this change(as suggested by your previous comment) at least in debug mode if i do step operation ,i could run the SW after words.

Now with this change control is not coming out or going into of this function even after step operations.

Attached screenshot,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thank you once again. I've obviously missed this part of the documentation, sorry for that.

Kind regards,

Joey