- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Pflash completeness check

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear

We use an S32K144 MCU and play to check if the code is completeness when power on every time. Now we calculate CRC of checksum and save the value at then end of Flash. And Read every byte of flash of all the setting address when power on. Compare the saved checksum and new calculated checksum. But it cost too much time. About 40ms now.

Do we have an hardware method to get the same purpose to check if the Flash are the same as Programed(No damaged)

Thanks you very much.

Charles

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Charles,

I can see two options:

1. Use Secure boot function which checks the flash content.

https://www.nxp.com/webapp/Download?colCode=AN5401

https://www.nxp.com/webapp/Download?colCode=AN5401SW

See chapter "4.4 Secure Boot"

2. Another option is to use DMA and CRC module. DMA can feed the CRC on background, so you will not lose so much time.

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lukas

Thank you very much. Do we also have an example for DMA or CRC?

Thank you again.

Charles

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Charles,

I wrote such example for MPC5748G:

There's the same DMA module, so you can see how to configure the DMA. CRC module is very simple module, there shouldn't be a problem.

Then there's set of examples (including DMA) for S32K in this application note:

https://www.nxp.com/docs/en/application-note/AN5413.pdf

The zip file is currently not available on the web, so I will attach it here.

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lukas

I find another example (Which is the same type MCU with mine):

https://community.nxp.com/docs/DOC-332957

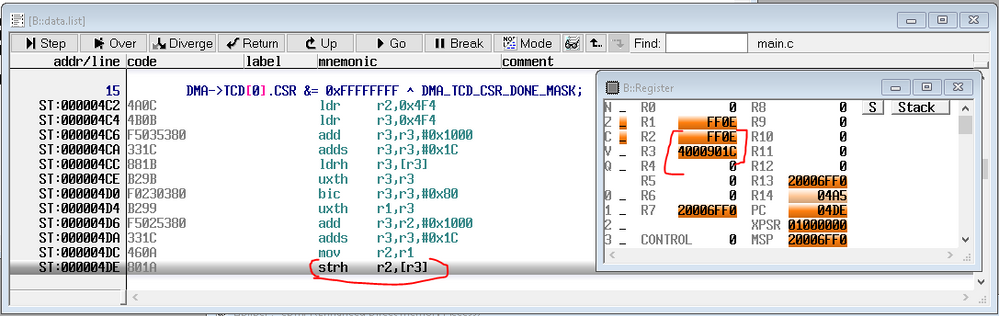

But every time when I step run to :

DMA->TCD[0].CSR &= 0xFFFFFFFF ^ DMA_TCD_CSR_DONE_MASK; // Clear Channel Done flag

it will goes to HardFault_Handler. DO you have good suggestion why it runs this fault?

Note: I copy the DMA related information from this example to my project.

Thanks

Charles

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Charles,

not sure what's going on. Do you have some simple project which could be shared? I can check it.

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lukas

How can I send you attachment?

Our project is too big. I can send you the code I add from DMA in our project.

Thanks

Charles

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

attachment can be added directly to a post, just click on "Use advanced editor" on the right side of "Reply" window.

You can also double check used address and value when writing the TCD.CSR. It should be address 0x4000901C and the value depends on original value with cleared DONE bit. I can see in my debugger:

Or do you use memory protection unit? Are other writes to TCD working?

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lukas

Thanks. eDMA works my local now. I am trying to use CRC now. Still have two parts need your help.

1. CRC config error. After the first line config below, any code I put in the second line will go to HardFault_Handler. Very stange

2. I want to calculate all the Pflash CRC. How Can I control the total bytes transfer from eDMA to CRC? Or no bytes limit for CRC?

3. By the way I also try to update the result CRC to Flash if not equal. The most less bytes to update Pflash is 8bytes?

Thank you very much.

Charles

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Charles,

1. Take a look at SW example in AN5413:

https://www.nxp.com/docs/en/application-note/AN5413.pdf

I can see that the zip file associated with this application note is not available on the web now for some reasons, so I will attach it here. Have you enabled clocks to CRC module? This seems to be the reason. You can see that in the example.

2. There's no limit for CRC module.

3. Yes, that's due to ECC. Anytime you program a phrase (8 bytes), ECC is calculated for this phrase and it's stored together with the data to flash. This also means that we are not allowed to program phrase which is not fully erased - this would corrupt the ECC.

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lukas

Thanks, you are correct. I miss the clocks. And reconfig it base on the datasheet. CRC works.

They are all 16bits now. I am trying 32bits. But seems DMA config always not work.

WHen I update above from 16bits to 32bits. It can not read out any data.

Regards

Charles

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Have you updated also NBYTES parameter? It was 2 in previous configuration, should be 4 now. Please give this a try.

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lukas

Yes, DMA can read 4 bytes now.

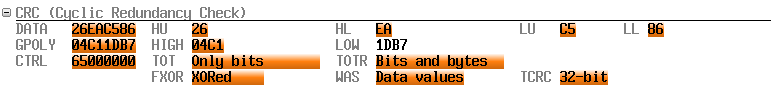

WHen I caculate CRC. It seems the value not match the result.

PCC_CRC->PCCn |= PCC_PCCn_MASK;

CRC->CTRL = CRC_CTRL_TCRC(1)|CRC_CTRL_TOTR(0)|CRC_CTRL_TOT(0);

CRC->GPOLY = 0x04C11DB7;

CRC->CTRL = CRC_CTRL_TCRC(1) | CRC_CTRL_TOTR(0)|CRC_CTRL_TOT(0)|CRC_CTRL_WAS(1);

CRC->DATAu.DATA = 0xFFFFFFFF;

CRC->CTRL = CRC_CTRL_TCRC(1) | CRC_CTRL_TOTR(0)|CRC_CTRL_TOT(0)|CRC_CTRL_WAS(0);

CRC->DATAu.DATA = 0x00260020;

u16DestBuffer1[15]=(CRC->DATAu.DATA);

And the result u16DestBuffer1[15] =0x 60E11069

while the result from On-line CRC calculation and free library and Vector hex view are all 0x26EAC586

I don't know why. Please help

Regards.

Charles.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Charles,

it depends on settings in CTRL register. I got the same result when used these settings:

Regards,

Lukas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lukas

I come to this topic again.

It works perfect till now with EDMA and CRC module to calculate whole flash CRC32.

My new question S32K144 is 32-bits CPU. Our original method is read from flash bytes and bytes (with out EDMA). Which cost too much time. Why EDMA can so fast? It doesn't use same 32bits wire width?

Charles

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Lukas

It works. Thank you very much.

Best Regards

Charles