- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Here am with S32K 148 EVB & here am with 6 sensors(slaves) that need to communicate over SPI channel, As I see S32K will support only 4 chip selects, how to achieve communication with 6 sensors ? (am using SPI PAL drivers from processor expert configuration).S32K 148 is the master.

Also can some one provide me the example on LPSPI multi master configuration on same SPI channel (SPI0).

Thank you in advance !

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Which SDK version do you use?

The LPSPI_DRV_SetPcs() function takes 3 parameters including PCS polarity.

Please step the function and double-check if the TCR command (which_pcs, polarity) is correct.

Thanks,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

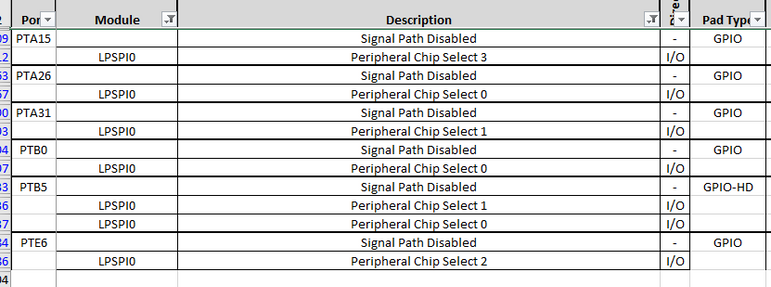

The LPSPI0 module supports only 4 PCS.

But the S32K148 MCU has 6 LPSPI0 PCS pins.

So you could use all of the PCS pins.

For example LPSPI0 PCS0 can be either PTA26 or PTB0.

The port module would need to be reconfigured so that the LPSPI0 module can control the correct pin before a transfer is triggered.

We don't have such an example though.

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thankyou for the response

But re initialising the port pins at the run time may cost the time.

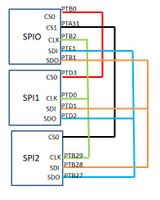

Here I have attached my code , in which SPI0 is the master and SPI1 and SPI2 are the slaves , if am communicating alone with SPI1 or SPI2 it is working fine able to send & receive data properly. but if SPI1 and SPI2 sharing the SDI & SDO, SCLK lines of SPI0 then am seeing master received data is "255".

uint8_t master_send[BUFFER_SIZE] = {1, 2, 3, 4, 5, 6, 7, 8, 9, 10};

uint8_t master_receive[BUFFER_SIZE];

uint8_t slave_send[BUFFER_SIZE] = {1, 2, 3, 4, 5, 6, 7, 8, 9, 10};

uint8_t slave_receive[BUFFER_SIZE];

volatile uint8_t i = 0;

uint8_t frame_sent = 1;

volatile uint32_t swt = 0;

CLOCK_SYS_Init(g_clockManConfigsArr, CLOCK_MANAGER_CONFIG_CNT,g_clockManCallbacksArr, CLOCK_MANAGER_CALLBACK_CNT);

CLOCK_SYS_UpdateConfiguration(0U, CLOCK_MANAGER_POLICY_AGREEMENT);

PINS_DRV_Init(NUM_OF_CONFIGURED_PINS, g_pin_mux_InitConfigArr);

PINS_DRV_ClearPins(GPIO_LED, RED_LED);

/* Initialize SPI0 */

SPI_MasterInit(&spi1Instance, &spi1_MasterConfig0);

//SPI_MasterInit(&spi1Instance, &spi1_MasterConfig1);

/* Initialize SPI1 */

SPI_SlaveInit(&spi2Instance, &spi2_SlaveConfig0);

//SPI_SlaveInit(&spi3Instance, &spi3_SlaveConfig0);

PINS_DRV_SetPins(GPIO_LED, GREEN_LED);

OSIF_TimeDelay(500);

PINS_DRV_ClearPins(GPIO_LED, GREEN_LED);

while(1)

{

SPI_SlaveTransfer(&spi2Instance, slave_send, slave_receive, NUMBER_OF_FRAMES);

SPI_MasterTransferBlocking(&spi1Instance, master_send, master_receive, (uint8_t) NUMBER_OF_FRAMES, (uint8_t) TIMEOUT);

/* verify that the data received is correct */

frame_sent = 1;

for(i = 0U; i < BUFFER_SIZE; i++)

{

if((slave_send[i] != master_receive[i]) || (master_send[i] != slave_receive[i]))

{

frame_sent = 0;

break;

}

}

if(frame_sent == 0)

{

//PINS_DRV_SetPins(GPIO_LED, BLUE_LED);

PINS_DRV_ClearPins(GPIO_LED, BLUE_LED);

}

else

{

PINS_DRV_SetPins(GPIO_LED, BLUE_LED);

//PINS_DRV_ClearPins(GPIO_LED, BLUE_LED);

}

SPI_SetSS(&spi1Instance, spi1_MasterConfig1.ssPin);

SPI_SlaveTransfer(&spi3Instance, slave_send, slave_receive, NUMBER_OF_FRAMES);

SPI_MasterTransferBlocking(&spi1Instance, master_send, master_receive, (uint8_t) NUMBER_OF_FRAMES, (uint8_t) TIMEOUT);

/* verify that the data received is correct */

frame_sent = 1;

for(i = 0U; i < BUFFER_SIZE; i++)

{

if((slave_send[i] != master_receive[i]) || (master_send[i] != slave_receive[i]))

{

frame_sent = 0;

break;

}

}

if(frame_sent == 0)

{

PINS_DRV_SetPins(GPIO_LED, RED_LED);

//PINS_DRV_ClearPins(GPIO_LED, RED_LED);

}

else

{

//PINS_DRV_SetPins(GPIO_LED, RED_LED);

PINS_DRV_ClearPins(GPIO_LED, RED_LED);

}

}

Small observation here all the time am seeing Slave side CS pin (SPI1) is high even after SPI transaction.

attached processor expert configuration screen shots

Thanks in advance

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Which SDK version do you use?

The LPSPI_DRV_SetPcs() function takes 3 parameters including PCS polarity.

Please step the function and double-check if the TCR command (which_pcs, polarity) is correct.

Thanks,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

am using S32K148_SDK 3.0.0

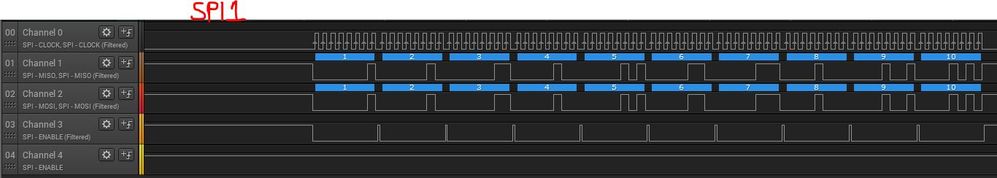

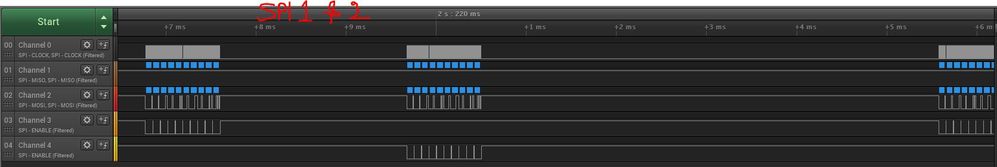

Yes, in debug mode cross verified the TCS register it is updating as per requirement. Even in the logic analyser we can see CS is working as expected & even MOSI line also working as expected.

But MISO is line is continuously high.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

It seems like the slave modules do not detect the PCS.

All I see from the attachments is that the slave modules are routed to 2 PCS each in PORT.

But are the slave modules configured to the correct PCS in LPSPI?

Also, get the status of the slave transfers with LPSPI_DRV_SlaveGetTransferStatus().

Thanks,

BR, Daniel