- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Hello,

I have a question regarding the configuration of the MC_ME module to select the FIRC clock for FlexCAN in S32K314.

[Figure1]

As shown in [Figure1], it is mentioned that the status of the FIRC can be checked through BLOCK52 in MC_ME1.

[Figure2]

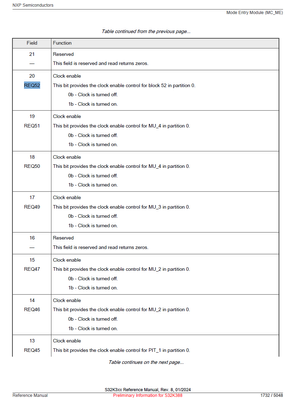

In [Figure2], it is shown that the clock for Block52 can be configured.

[Figure3]

However, when I checked the S32K314.h file [Figure3], I couldn't find the bit named REQ52. How can I configure this setting?

已解决! 转到解答。

Hi @malove

I have compared different versions of development packages and it seems that the headers may vary depending on the version of the development package, could you help me with the information of the version you are using?

Hi @malove

FIRC is enabled by default and we understand that the Table 260 (MC_ME partition peripheral mapping and clock control) of the RM may lead to the conclusion that FIRC can be enabled like the other clocks (MC_ME->PRTN1_COFB1_CLKEN), but it was found that configure FIRC causes hard fault in run mode with debugger disconnected. Therefore the register was set to reserved.