- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Software Forums

- :

- S32 SDK

- :

- Re: S32K116 PWM generation using FLEXIO - Cannot set duty cycle to 0

S32K116 PWM generation using FLEXIO - Cannot set duty cycle to 0

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K116 PWM generation using FLEXIO - Cannot set duty cycle to 0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello there,

I am currently working on a project using FLEXIO to emulate the PWM generation.

Here is the problem I am facing:

When I am trying to stop PWM generation for the duty cycle 0 case, I cannot do that. It outputs the clock fed to the FLEXIO instead of the voltage low.

As the application note AN12174 suggests 'flexio_pwm_stop() function disables the timer0 by setting TIMOD and disable generating the PWM.' I set TIMOD to 0 when the duty cycle is equal to 0.

Here is my code for reference:

if(duty > 0)

{

/*!

* FlexIO Timer Control:

* ============================

*/

FLEXIO->TIMCTL[0] |=

FLEXIO_TIMCTL_TIMOD(2) /* Dual 8-bit counters PWM high mode */

|FLEXIO_TIMCTL_PINSEL(0) /* Select FXIO_D0 */

|FLEXIO_TIMCTL_PINCFG(3); /* Timer pin output */

low = ( ( ( (4000000/20000) * (100-duty)) / 100) - 1) << 8;

high= ( ( (4000000/20000) * duty) / 100) - 1;

FLEXIO->TIMCMP[0] = high | low;

}

else

{

FLEXIO->TIMCTL[0] |=

FLEXIO_TIMCTL_TIMOD(0) /* Timer Disabled. */

|FLEXIO_TIMCTL_PINSEL(0 /* Select FXIO_D0 */

|FLEXIO_TIMCTL_PINCFG(3); /* Timer pin output */

}

Very appreciated for the help.

Thank you,

Junxi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Junxi,

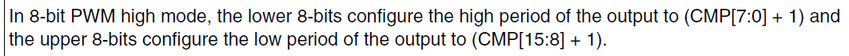

I'm not sure if I understand the question, but if you need an explanation why the duty cycle cannot be set to 0%, this is given by the operation of the 8bit PWM mode (54.3.1.21 Timer Compare N Register (TIMCMP0 - TIMCMP3)):

Regarding the AN12174 recommendation, do you have any problems with this approach?

Thanks,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daniel,

Thank you for the response. Sorry for the confusion. Let me clarify it.

What I want to achieve is when the duty cycle is 0, the PWM output should be at voltage level low always.

My PWM is using FLEXIO which fed by SIRCDIV2_CLK (4MHz), the frequency is 20kHz.

My first approach is as what you said, set FLEXIO->TIMCMP[0] = 0x0000 to configure the comparison counter to be 0.

So I set the duty cycle of the PWM to be 50% first to get a 20kHz, 50% duty cycle PWM. Then I set the duty cycle to be 0 by setting FLEXIO->TIMCMP[0] = 0x0000

However, when the TIMCMP[0] = 0, I measured a PWM with 2MHz and 50% duty cycle on my oscilloscope instead of a straight line at 0v.

Then my second approach is to disable the timer0 by setting TIMOD to 0.

So I repeat the sample step as above, after I set the duty cycle to 50%, I can see the TIMOD bit of TIMCTL0 set to be 2, and PWM generated correctly.

Then I tried set duty cycle to 0 by set TIMOD bit of TIMCTL0 to be 0 to stop the PWM.

However, it doesn't all me to configure the TIMOD again. It stays at 2.

And the PWM is still at 50% duty cycle instead of getting off.

Could you please let me know if I did something wrong?

Thank you,

Junxi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @junxi_cai,

I have been testing it today.

It works with this configuration:

FLEXIO->SHIFTCTL[0] |= (1 << 7); // PINPOL = 1, Pin is active low

Can you test it on your side?

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daniel,

Sorry for the late response. I also tried that, it is not get set to Low.

Instead, I use the clear register API to clear the TIMCTL register as below to solve the problem.

REG_BIT_CLEAR32(&FLEXIO->TIMCTL[ChannelNumber],0xFFFFFFFFu);

Thanks a lot.