- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- ソフトウェア・フォーラム

- :

- S32 SDK

- :

- Gap between two buffers in SCLK I2S

Gap between two buffers in SCLK I2S

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Gap between two buffers in SCLK I2S

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

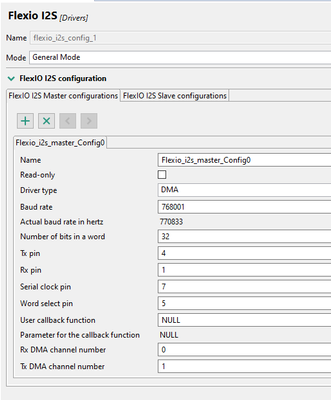

I'm using S32K142 controller for I2S communication.

I configured I2S through SDK drivers and sending audio buffer continously.

below is screenshot in which we are facing gap in SCLK and due to that other clocks are being disturbed.

configuration:

using following function to send data in infinite loop.

uint8_t I2S_DataBuff_u8[] = {0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA,0xAA};

FLEXIO_I2S_DRV_MasterSendData(&I2SMasterState, I2S_DataBuff_u8, 32U);

please share solution , how can I continuous send data.

Regards,

Mohit

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @Mohit_Manvar,

It has been discussed here:

https://community.nxp.com/t5/S32K-Knowledge-Base/S32K3-FlexIO-I2S-Continuous-Transfer/ta-p/1692165

Unfortunately, we don't have such an example built with the SDK, but in principle, it is the same.

A baremetal example is attached.

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @danielmartynek ,

Thanks for sharing bare metal code.

I tried to import code and build but it is not building successfully. error is attached below.

additionally if Build for release it is building successfully.I tried to check issue for debug_flash mode but following issue it there

so I tried with S32Ds for ARM IDE but having same problem.

please share details how can I remove error.

Regards,

Mohit Manvar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mohit,

In S32DS 3.5, create a new project (without SDK) and copy the cource code from the example.

It should work this way.

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

yes,It is now building.

but during executing code , it is automatically going to Default ISR from below line.

I'm using S32K144 EVB for debugging.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @Mohit_Manvar,

I haven't had the time to test it.

Is it fault exception?

Please implement HardFault_Handler() in the project.

https://community.nxp.com/t5/S32K-Knowledge-Base/Fault-handling-on-S32K14x/ta-p/1114447

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I tried to check causing of fault and I got this.

please briefly explain where should I call fault handler in code and how can I use it?

if possible please configure at your side and revert me back.

Mohit

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello experts,

please help out to resolve this open topic.

Best regards,

Mohit

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @Mohit_Manvar,

I'm sorry for the delay. I see now that the project has been built for the first maskset of S32K144 where DMA clock could be gated in PCC[CGC]. This was removed on the current version of the MCU.

Just comment this line out:

// PCC->PCCn[PCC_DMA0_INDEX] |= PCC_PCCn_CGC_MASK;

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I tried to comment out that line but at the end it is not giving output for I2S.

Does any other modifications needed?

output pins:

please suggest your thoughts.

Mohit

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @Mohit_Manvar,

Unfortunately, we don't have the capacity to port and debug every example right now.

The examples are provided AS IS.

Regards,

Daniel