- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 软件论坛

- :

- S32 Design Studio

- :

- Re: Use of ADC0 and ADC1 both with software trigger

Use of ADC0 and ADC1 both with software trigger

Use of ADC0 and ADC1 both with software trigger

Hi,

I want to acquire the voltage measurements of two signals. My question is:

is it correct to use both ADC0 and ADC1 with software trigger for the acquisition of two signals?

Thanks

Best regards

Paola

Thank Daniel.

I used these functions:

void SlowRUNmode_FIRC_48MHz(void)

{

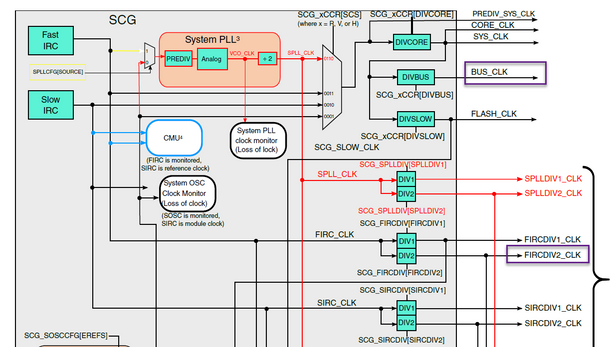

SCG->RCCR=SCG_RCCR_SCS(3) /* FIRC as clock source*/

|SCG_RCCR_DIVCORE(0b00) /* DIVCORE=0, div. by 1: Core clock = 48/1 MHz = 48 MHz*/

|SCG_RCCR_DIVBUS(0b00) /* DIVBUS=0, div. by 1: bus clock = 48 MHz*/

|SCG_RCCR_DIVSLOW(0b01); /* DIVSLOW=1, div. by 2: SCG slow, flash clock= 24 2/3 MHz*/

while (((SCG->CSR & SCG_CSR_SCS_MASK) >> SCG_CSR_SCS_SHIFT ) != 3) {}

/* Wait for sys clk src=FIRC */

}

void FIRC_init_48MHz(void)

{

SCG->FIRCCSR = 0x00000000; //FIRCCEN=0: SIRC is disabled (default) for write

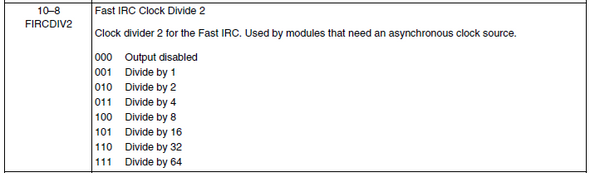

SCG->FIRCDIV = 0x00000101; //FIRCDIV1 & FIRCDIV2 divide by 1, max in HSRUN/RUN is 48MHz

SCG->FIRCCFG = 0x00000000; //Range 48MHz

SCG->FIRCCSR = 0x00000001; //LK=0: FIRCCSR can be written

//FIRCCEN=1: Enable SIRC, FIRCSEL = 0 ->Fast IRC is not the system clock source

while(!(SCG->FIRCCSR & SCG_FIRCCSR_FIRCVLD_MASK)); // Wait for FIRC valid

}

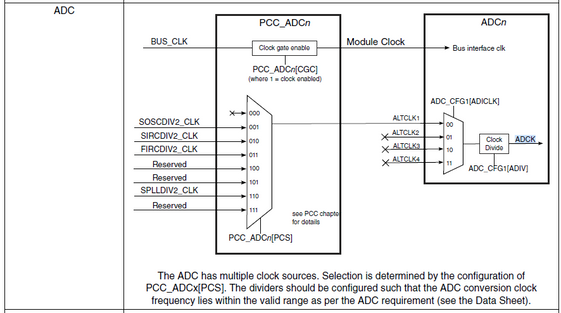

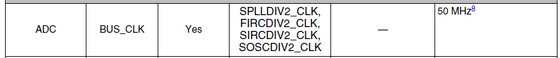

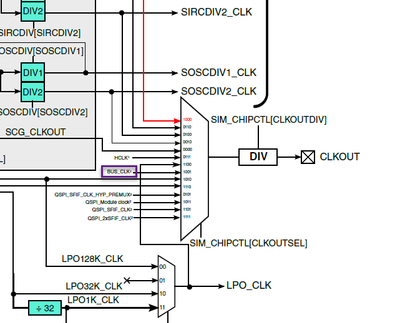

As mentioned in RM (pag.541) when there is FIRC clock it is should set the slow run mode. With the functions that I wrote above, I have the Bus Clock equal to 48MHz and the clock of ADC equal to FIRCDIV2 that is equal to 48MHz with ADIV = 0.

In this configuration I should have both fADC, fBUS equal to 48MHz. I would know if the configuration for FIRC clock is correct in order to have a correct conversion time from the formula of ADC.

Best regards

Paola

Thanks Daniel.

Finally I have the last question

5000*(adc_result)/(4095) (4095 is (2^12) -1 because I set as the resolution 12)

In CAN message when there is a dominant Bit (0) on CAN-High there will be as voltage 3.5V and on CAN-Low 1.5V. So in my configuration, every time that there is a 0 bit the ADC gives as result voltage measurements that aren't close to 3.5V and 1.5V.

Why does the ADC give a incorrect value? What is the justification?

Thanks for your help

Best regards

Paola

Hi Paola,

Please open a new thread for each addition question that is not related to the topic of this one (ADC SW trigger).

Have you tried measuring a constant voltage to test the ADC?

Is the ADC module calibrated?

The internal ADC sample and hold capacitor might not be charged to the input voltage if the sample time is too short or the input resistance is too high.

Regards,

Daniel

Hi Paola,

You didn't specified the MCU.

But if you use S32K1xx, then yes, both ADC0 and ADC1 can be triggered by a write to SC1A (when SC2[ADTRG]=0) and sample different signals.

Regards,

Daniel

Thank you Daniel.

I use s32k144 and both for ADC0 and ADC1 the software trigger.

Daniel sorry for my trivial question but I would ask you the following thing:

if I select as the clock of ADC FIRCDVI2 [PCC->PCCn[PCC_ADC0_INDEX] |= PCC_PCCn_PCS(3)], it is necessary to set the slow run mode in order to obtain as the core_clk and the bus_clk 48MHz.

In term of conversion time of ADC, this means that the fADC and fBUS is equal to 48MHz. Is it correct?

Thank you