- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- S12 / MagniVマイクロコントローラ

- :

- Re: Machine exception

Machine exception

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Machine exception

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

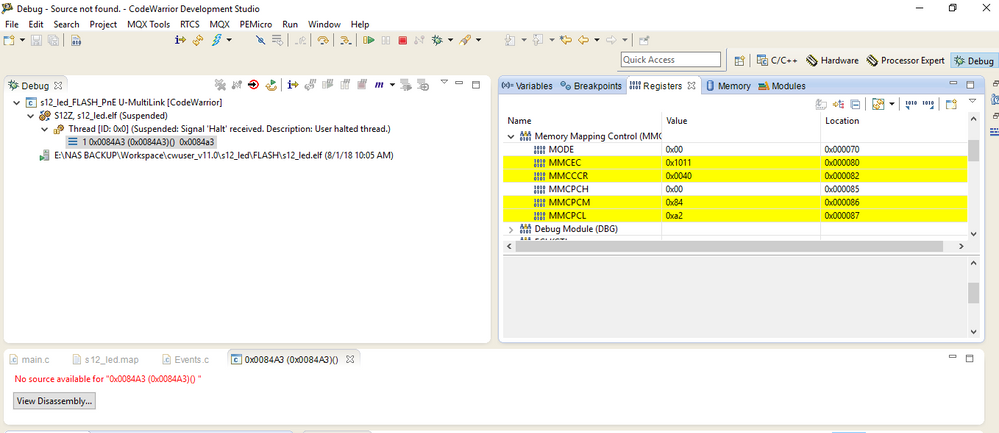

I am using s12zvml31 controller. When i tried to debug my software the machine exception occurs and i saw the datasheets and checked the registers mmcec and mmccc,

Error code register

Bit Field Values:

ITR bits[ 15:12 ] = 1 S12ZCPU

TGT bits[ 11:8 ] = 1

ACC bits[ 7:4 ] = 1 Opcode fetch

ERR bits[ 3:0 ] = 1 Access to an ilegal address range

Captured S12ZCPU Condition Code Register

Bit Field Values:

CPUU bits[ 15:15 ] = 0

bits[ 14:14 ] = 0

bits[ 13:13 ] = 0

bits[ 12:12 ] = 0

bits[ 11:11 ] = 0

bits[ 10:10 ] = 0

bits[ 9:9 ] = 0

bits[ 8:8 ] = 0

bits[ 7:7 ] = 0

CPUX bits[ 6:6 ] = 1

bits[ 5:5 ] = 0

CPUI bits[ 4:4 ] = 1

bits[ 3:3 ] = 0

bits[ 2:2 ] = 0

bits[ 1:1 ] = 0

bits[ 0:0 ] = 0

I have tried the exception handler by writing CPMUARMCOP register to reset the controller and Im not writing any instruction at last 8 bytes of RAM, ROM. Am I missing anything?

Please help me to found out.

Regards

kaarthi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

You should start inspecting code at address MMCPC points to. Perhaps some legacy code expects 16 bits code pointers and does some ptr-int-ptr conversions?

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Edward,

I checked the Kaarthi's code and the machine exception occur after enabling interrupts in the PE init function and Kaarthi recognizes that exception did not occur when the timer interrupt is disabled.

Best regards,

Diana

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Diana,

OK, then either interrupt vector is wrong, or ISR does something wrong. In first case address in MMCPC contains no useful information, in 2nd it may point to address with buggy code.

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Edward and Diana,

The timer interrupt doesn’t have problem, because I have tried several ways to find the problem and with or without timer interrupt I see no difference, the other functions only making a part.

Note: I said that “exception did not occur when the timer interrupt is disabled” only with no other functions because I wanted to check whether the problem is with that interrupt or others.

I hope you understand.

Regards

kaarthi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Edward,

I checked the address that pointed by MMCPC register and that address points to non accessible memory of controller and cross checked the .map file, there is no such address.

Regards

Kaarthi

Sent from my Sony Xperia™ smartphone

-

kef2 wrote -

NXP Community <https://community.freescale.com/resources/statics/1000/35400-NXP-Community-Email-banner-600x75.jpg>

Re: Machine exception

reply from Edward Karpicz<https://community.nxp.com/people/kef2?et=watches.email.thread> in S12 / MagniV Microcontrollers - View the full discussion<https://community.nxp.com/message/1040667?commentID=1040667&et=watches.email.thread#comment-1040667>

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kaarthi ,

I'll experiment later at free time how S12Z exceptions behave (MMCPC and status bits) on bad interrupt vector perhaps due to accidental overwrite of IVBR, or jump to wrong address or return to wrong address due perhaps stack overflow.

At now we have a lot of unknowns. Could you create copy project to share with sensitive IP removed but problem still shown? I could try figuring what's wrong on S12ZVC, I don't have S12ZVML.

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I tried a bit. On jump from buggy code to not implemented address

ITR bits[ 15:12 ] = 1 S12ZCPU

TGT bits[ 11:8 ] = 0 <---- different to yours

ACC bits[ 7:4 ] = 1 Opcode fetch

ERR bits[ 3:0 ] = 1 Access to an ilegal address range

and MMCPC points exactly to CPU instruction, which performed wrong jump.

On servicing interrupt while interrupt vector points to non implemented address or pointing to registers space (TGT==1), MMCEC is exactly as you wrote, all MMCEC fields = 1, MMCPC points to unrelated address. Issuing SWI with bad SWI vector MMCPC shows FFFFF0. I didn't check whether it changes servicing different interrupt vectors.

So please double check your interrupt vectors and perhaps IVBR.

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Edward,

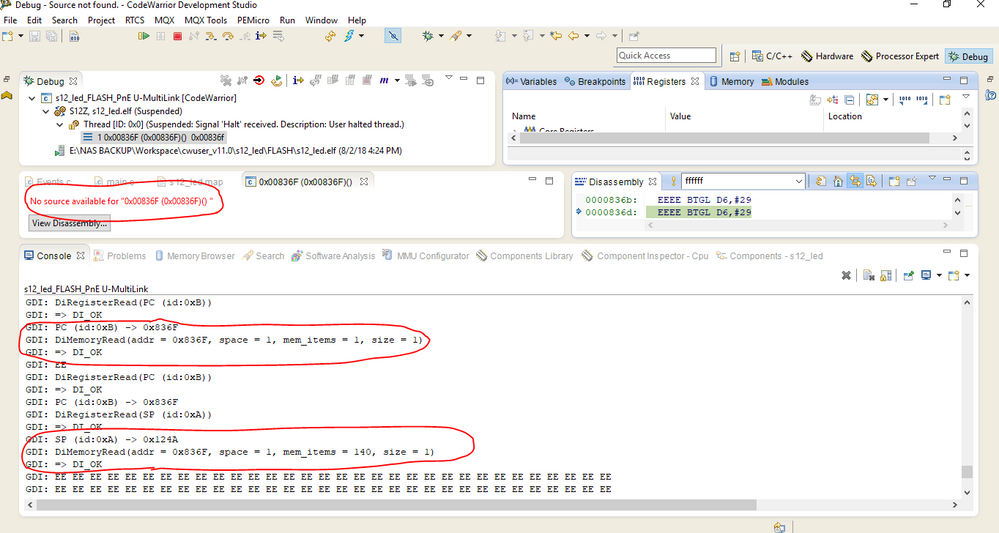

I attached a screenshot of register value when I get exception and check the MMCPC register, it is actually a non-accessible memory.

And I removed all the interrupts from my code.

Regards

kaarthi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Well, some debugging is required, a waste of time without the code, sorry

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kaarthi,

Such simple error and such bizarre behavior. Why MMCPC showed weird address about 0x008xxx? Because your code is at about 0xFF8xxx. Why no leading FF in MMCPC? Because not nice coding error made top byte of return address overwritten with 00.

See in events.c

GLOBAL VOID ReadInputs(VOID)

{

BYTE data[1],changed_mask,i;

Size of data array is 1, yet you loop assumes data size 2:

for (i = 0; i < 2; ++i)... data[i]

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Edward,

I corrected that bug but still I’m getting the problem. For testing I even tried without that function, but problem continues.

Regards

kaarthi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

then it is another problem. How could I reproduce it?

You code in *.rar worked with periodic interrupt bean disabled. Once enabled it quickly run into exception. Fixing data[1]->data[2] issue solved it completely. Perhaps just on my s12zvc? Not possible to reproduce - not possible to fix.

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank Edward,

As you said once you enabled the interrupt it ran to exception, is there anything wrong in vector allocation?

Regards

kaarthi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

No. The only problem was BYTE data[1], which had to be fixed to data[2].

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Edward,

Thanks for your support.

I finally got the issue solved somewhat.

Now I’m working in ADC part in this controller and I have the doubt in this.

I have wrote those command sequence lists and result sequence lists and configured the GDU peripheral and PTU. When will the ADC interrupt occur? Does it require any trigger from PTU and when will the conversions start?

Regards

kaarthi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

ADC command list is where you set after which conversion to trigger interrupt. IIRC you need to bitwise or your command long word with (1L << 24) to trigger interrupt.

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Edward,

The ADC error interrupt has occurred with restart error and I used PTU to give the trigger to ADC and PTU reload error has occurred..

Regards

Kaarthi

Sent from my Sony Xperia™ smartphone

-

kef2 wrote -

NXP Community <https://community.freescale.com/resources/statics/1000/35400-NXP-Community-Email-banner-600x75.jpg>

Re: Machine exception

reply from Edward Karpicz<https://community.nxp.com/people/kef2?et=watches.email.thread> in S12 / MagniV Microcontrollers - View the full discussion<https://community.nxp.com/message/1045390?commentID=1045390&et=watches.email.thread#comment-1045390>

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Edward,

I wanted to add ADC1 AN1_3.

And then, I modified a code

volatile char ADC0CommandList[6][4] @0x00001000 = {

{0x40,0xD0,0x00,0x00},

{0xC0,0xCB,0x00,0x00},

{0x00,0x00,0x00,0x00},

{0x00,0x00,0x00,0x00},

{0x00,0x00,0x00,0x00},

{0x00,0x00,0x00,0x00}

};

volatile char ADC1CommandList[6][4] @0x00001018=

{

{0x40,0xCA,0x00,0x00},

{0xC0,0xD3,0x00,0x00},

{0x00,0x00,0x00,0x00},

{0x00,0x00,0x00,0x00},

{0x00,0x00,0x00,0x00},

{0x00,0x00,0x00,0x00}

};

volatile short PTUTriggerEventList[2][2][3] @0x00001048 =

{

{{0x0100,0x0200,0x0000},{0x0000,0x0000,0x0000}},

{{0x0100,0x0200,0x0000},{0x0000,0x0000,0x0000}}

};

Now Im getting ADC0 and ADC1 trigger error.

How to set the correct configuration?..

Regards

kaarthi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I tried again the problem continues here but when I removed DisplOut function it works fine now.

kaarthi