- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- Re: I-bit feature implementation on S12Z magniV

I-bit feature implementation on S12Z magniV

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I-bit feature implementation on S12Z magniV

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have a question about S12Z MagniV(e.g.S12ZVM).

About interrupt, where I-bit mask/unmask feature is implemented?

On S12Z CPU? Or INT module?

I cannot find I-bit signal path on device RM and S12Z core manual.

Best Regards,

Ikki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ikki,

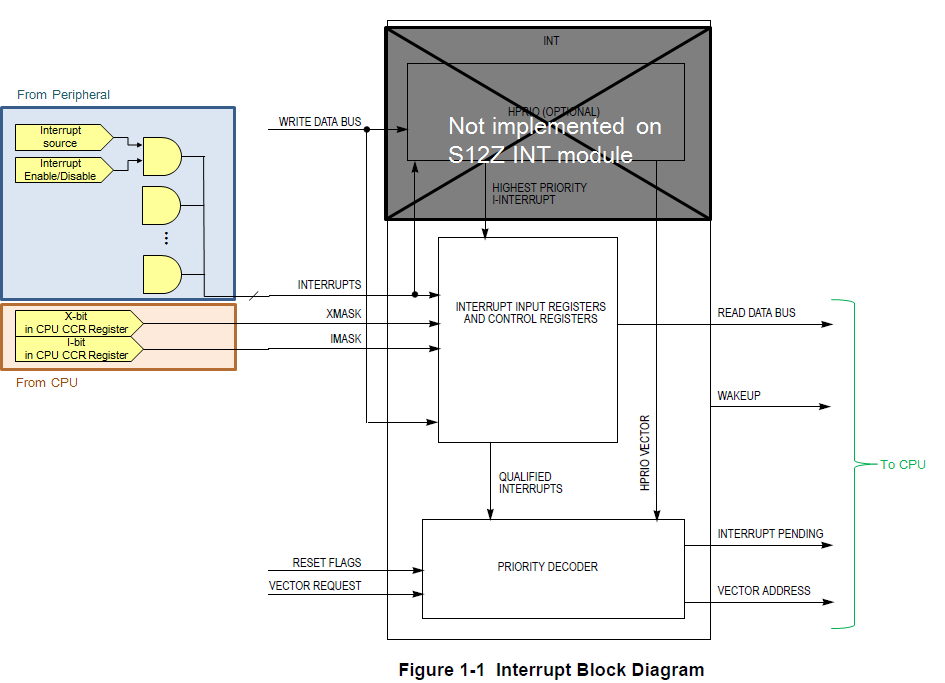

The I-bit is a part of CPU register CCR. The value of bit is connected to an interrupt module S12ZINTV0.

The picture is similar to previous MCUs, Figure 1-1 in http://www.nxp.com/files/microcontrollers/doc/ref_manual/S12INTV1.pdf

Best regards,

Ladislav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi lama,

From your commnent, I imagine the following signal path/connection.

My understanding summary:

1. SEI/CLI instructions act for CCR I-bit

2. I-bit set/clear status signal is connected to INT modules

3. I-bit set/clear status signal and each peripheral interrupt signal are muxed in INT modules

INT module judges Interrupt release or pending based on these signals and register settings

(e.g. PRIOLVL[2:0] in S12Z INT module)

4. Output signals are connected to CPU

Is my understanding correct?

If not, could you point out the wrong point/description?

Best Regards,

Ikki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ikki,

First of all I am sorry for delay because of vacation.

If I have not missed anything then your description is OK.

I have also asked Radek for double check.

BTW; I really do not understand why you need such an info. From user point of view it is enough to see it as a black box and just understand interrupt selection, nesting possibilities and setup.

Best regards,

Ladislav