- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 产品论坛

- :

- S12 / MagniV微控制器

- :

- Re: How to send break characters

How to send break characters

How to send break characters

We have a LIN-Motor Controller project recently and the microcontroller is selected S9S12ZVL. As a LIN-Master, we should send break which contains at least 13 logic 0s based on LIN2.1. We write a logic 1 to SBK(SCICR2) and BRK13(SCISR2), the M(SCICR1) keeps 0 as default. But the LIN bus is at high level all the time, it looks like that we failed to send break. However, We can receive and send datas by the LIN bus. Could you help us? Thanks.

Hi Jeff,

I suppose, that your question is connected to the next thread:

https://community.nxp.com/thread/451237

Correct?

We should toggle with SBK bit for transmitting break signal. For example:

SCI0CR2_SBK = 1; //START TO SEND

SCI0CR2_SBK = 0; //STOP SENDING BREAK

or

SCI0CR2 |= 0x01;

SCI0CR2 &= ~0x01;

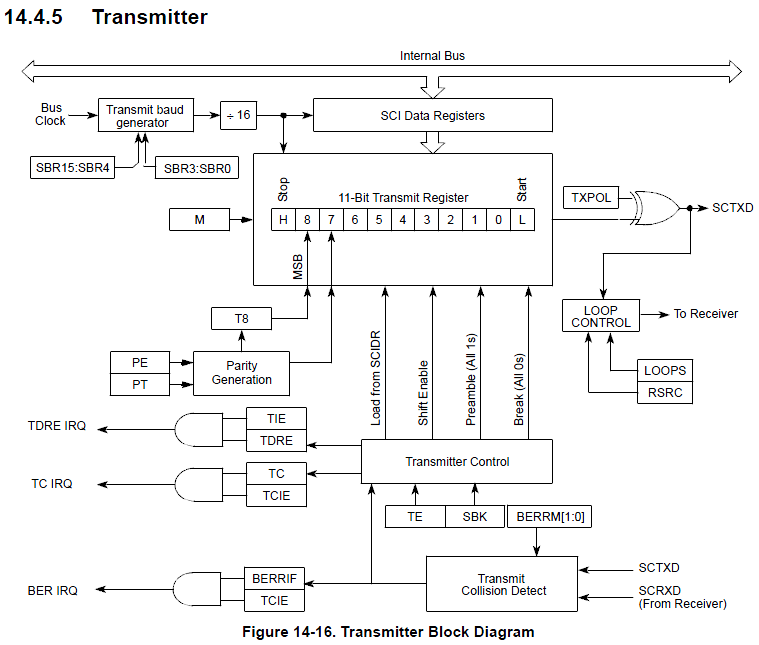

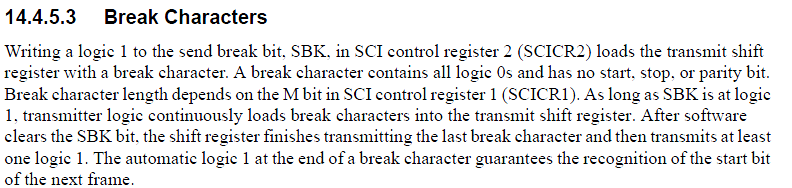

A break character contains all logic 0s and has no start, stop, or parity bit. As long as SBK is at logic 1, transmitter logic continuously loads break characters into the transmit shift register. After software clears the SBK bit, the shift register finishes transmitting the last break character and then transmits at least one logic 1. The automatic logic 1 at the end of a break character guarantees the recognition of the start bit of the next frame.

So, when we just set SBK bit without clearing SBK bit (as in the code in next thread), the SCI TX output will be kept in dominant level whole time. However, the LIN PHY has TxD-dominant timeout feature enabled by default. Therefore, the LIN transmitter will be shut down after a while and you will not see the dominant level at LIN pin.

Please check LPSR_LPDT flag.

There is the LIN stack:

http://www.nxp.com/assets/downloads/data/en/device-drivers/FSL_LIN_2.X_STACK.zip

The simple LIN example code for your inspiration (for the older S12G family) may be found here:

https://community.nxp.com/docs/DOC-93792

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Radek,

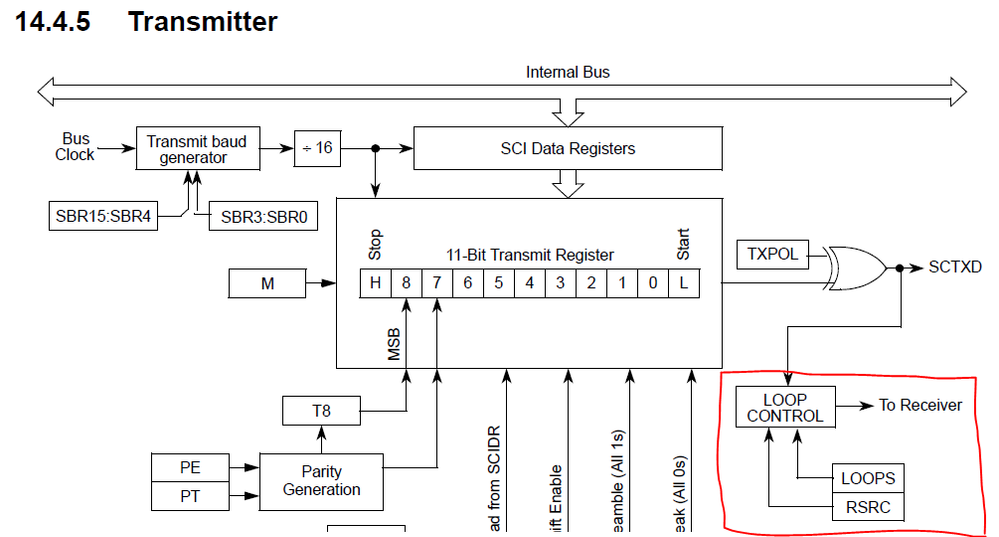

Thanks for your replay. After many attempts of us, we find that the LOOP CONTROL should be enble and enter into loop operation mode when you want to send break signal.

The configuration is:

SCI0CR1_LOOPS = 1;

SCI0CR1_RSRC = 1;

SCI0CR2_SBK = 1;

After you send break signal, you must clear SBK bit and switch back to normal operation mode before the next frame.

SCI0CR2_SBK = 0;

SCI0CR1_LOOPS = 0;

SCI0CR1_RSRC = 0;

Hi Jeff,

In fact, the LOOP CONTROL does not need to be enabled for sending break signal.

If you set SCI0CR1_LOOPS bit and clear SCI0CR1_RSRC bit, the transmitter output is internally connected to the receiver input. When you set both these bits, the transmitter output and receiver input are connected at pin level (Single-wire mode). None of these settings are valid for proper LIN communication.

If you are not able to receive break signal without loop mode, the issue might be in LIN transceiver (LIN PHY). When MCU something sends on TX pin connected to LIN transceiver, the same data should appear also on RX pin with some very small propagation delay.

Are you sure, that LIN PHY is correctly enabled and configured (no errors signalized)?

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------