- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- S12 / MagniVマイクロコントローラ

- :

- Re: Help,The GDU doesn't work!

Help,The GDU doesn't work!

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Help,The GDU doesn't work!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Q1:

Hi, I began to use S12ZVML in my project one year ago, it work well. but in recent Life Test, I meet some trouble.

Two controllers can't operate normally, I connected the mcu through P&E, found that the GDU went wrong(GDUF_GHHDF and GDUF_GHHDIF are set) and GUD cut off the output signal.

Refer to the s12zvm reference manual, It showed that "Voltage on pin HD is greater than VHVHDLA or VHVHDHA". But I get the ADC raw value from the internal adc channel(ADC1_Internal_3:GDU DC link voltage monitor),the register value is 34518(left aligned), it showed that:

Vhd = 34518 / 65536 * 25V =13.1V(in most data, for example Freemaster, shows that 25V is the range)

or Vhd = 34518 / 65536 * 60V =31.6V (in datasheet, because I set register GDU Phase Mux Register (GDUPHMUX) 0x00, it means: Pin HD selected , VHD / 12 connected to ADC channel)

which one is right?

P.S: I try to force clearing the bit(write 1 to GDUF_GHHDF ),but it didn't work. Can you help me to find the root cause of this error?

Q2:

I looked for all information about the Vsup in reference manual. It was described:

"The VSUP pin can be routed via an internal divider to the internal Analog to Digital Converter.

Independent of the routing to the Analog to Digital Converter, it is possible to route this voltage to a

comparator to generate a low or a high voltage interrupt to alert the MCU."

But it didn't give the exact ratio of the "internal divider", I guess that the divider ratio is 1/5 from some application notes or example code, is that right or maybe it is pointed out in some other place or other document?

Best regards!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Radek:

Thank you for your reply!

For Q1:In my board, every time I power on, even no motor connected, GDU went wrong.

So, do it mean that the GDU is damaged?

About the damage, can you give me some advise about what causes that GDUF_GHHDF and GDUF_GHHDIF are set?

Best regard!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Chen,

The GHHDF flag is set by hardware if a high voltage condition on HD pin occurs.

The GHHDIF flag indicate change of GHHDF flag (set by hardware if GHHDF is set or if GHHDS is cleared).

Could you please measure voltage directly at HD pin by multimeter/oscilloscope?

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am having the same problem. GHHDS is set. V_HD > V_HVHDLA

What could happen in the internal circuit that this case would occur?

Also, the voltage on the HD pin is same as the power supply voltage 12V for example.

Best Regards,

Hardik Karelia

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Hardik Karelia,

By register bit GDUCTR_GHHDLVL you may change between levels VHVHDLA(typ 21V) and VHVHDHA(typ 28.3V).

The GDU generates VGS voltage (typ. around 10V) for N-channel transistors which go above the VHD voltage level. Unfortunately, the break-down voltage for UHV_180nm technology is slightly above 40V.

So, if the voltage at HD pin plus charge-pump/bootstrap voltage exceeds this break-down voltage (Absolute maximum is specified as 42V), the MCU may be damaged. Therefore, the maximum VHD voltage is specified just for 20V (up to 26.6V, but only for a limited time).

I hope it helps you.

Best regards

Radek

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Chen,

About Q1)

There are at least two ways how to measure DC link voltage.

If you measure Internal_3 GDU DC link voltage monitor ADC channel, the VHD is divided by the internal divider by 5. So, the first voltage calculation is correct Vhd = (34518 / 65536) * 5V range * 5 as divider = 13.1V.

If you measure Internal_2 GDU phase multiplexer voltage ADC channel and you set GDUPHMUX = 0x00, the VHD is divided by the internal divider by 12.

The HD high voltage monitor assert trippoint low is around 21V and HD high voltage monitor assert trippoint high is around 28V. The trippoint is selectable by GDUCTR_GHHDLVL bit.

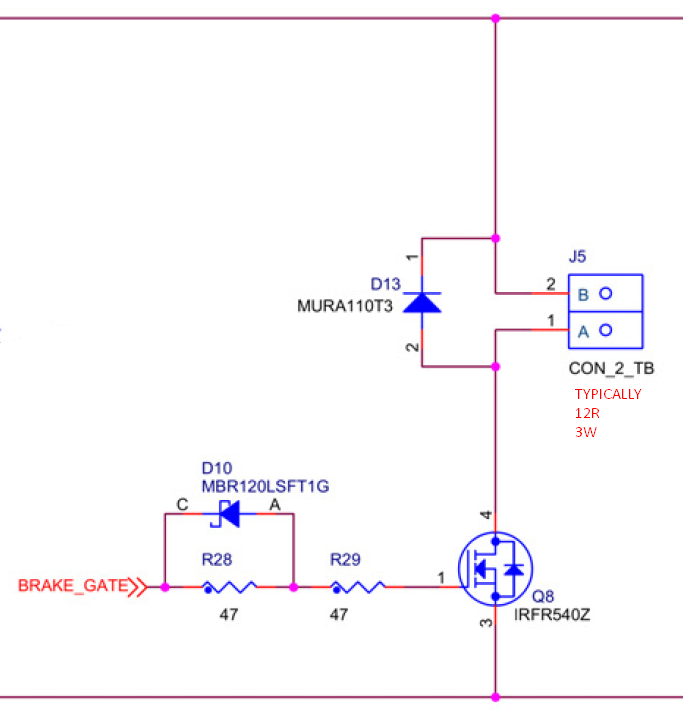

In general, the High HD voltage might be caused by fast decreasing of motor speed. In that case, we may use brake chopper circuit which will be enabled by MCU software when VHD across some dedicated level. An example of brake chopper circuit:

It is hard to say what is wrong with your board. Is that flag present also when you load the empty project into MCU? Power down/up helps or not?

Writing 1 to GDUF_GHHDF should clear that flag when VHD voltage is below VHVHDLD (typ. 20.5V) or VHVHDHD (typ. 27.9V) voltage level.

However, it is possible that the GDU is somehow damaged.

About Q2)

The VSUP voltage may be measured at Internal_4 BATS VSUP sense voltage ADC channel (available only at ADC0). The source for that ADC channel is BATS module. The voltage levels for comparators and Pin Input Divider Ratio is specified in Table G-1. Static Electrical Characteristics – BATS in RM

The BATS module may be configured for one of 4 available Low Voltage Warning levels and for one of two High Voltage Warning levels.

The input divider ratio for ADC measurement is 9.

I hope it helps you.

Have a great day,

Radek

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------