- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- Re: Using CPC as SRAM

Re: Using CPC as SRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Re: Using CPC as SRAM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hymalai,

You could use "Download" when create the bare board project, the debug program will be download at the effective address 0, so downloading program to DDR or SRAM depends on what kind of memory is mapped to effective address 0 in the initialization file.

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi!

Hello Hymalai,

You could use "Download" when create the bare board project, the debug program will be download at the effective address 0, so downloading program to DDR or SRAM depends on what kind of memory is mapped to effective address 0 in the initialization file.

Have a great day,

Yiping

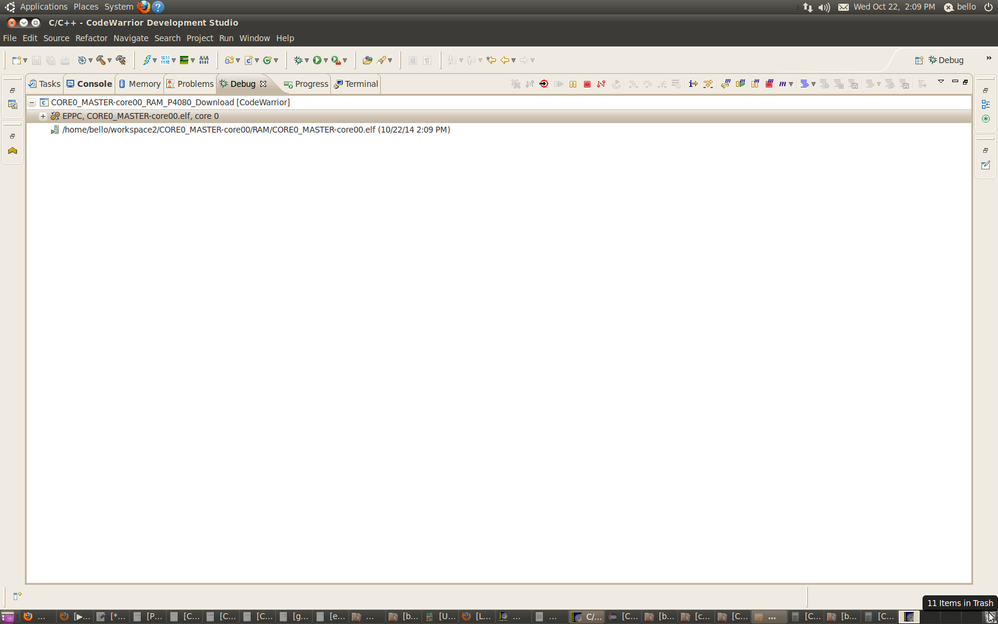

When I try to do that, the program do not debug. and SRAM is mapped to effective address 0 using law, and DDRs are disabled.

Thanks!

Regards,

Hymalai Bello

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hymalai,

In the default RAM lcf file P4080DS_gcc-eabi_core0.lcf, the stack and heap definitions are out of the range of 1M CPC as SRAM, and the TLB miss exception will be encountered. Please use SRAM version LCF file e500mc_gcc-eabi_SRAM.lcf, which I mentioned in the previous thread.

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi!

Can I use the registers for Partition allocation of CPC (CPC1_CPCPAR1....) when I am using CPC as SRAM? Is for assign a private space to each core.

thanks!

Regards,

Hymalai Bello

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hymalai,

The L3 CPC can be configured as:

SRAM

Unified, I-only, D-only

Locking (per Line)

I/O Stashing

Allocating logical Partition is needed if the L3 CPC block is configured for I/O Stashing.

If you would like to close this thread and discuss this topic in a new thread, please help to mark useful answers of this thread, thanks.

Thanks,

Yiping