- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

P2020 asleep pin not go low, P2020 cannot run

I have designed a board using P2020,the hardware config pins are connected to the CPLD,.The power up sequence is refer to the P2020RM.When the power up , 1) P2020 cannot be connected to the emulator(trace32) ,cannot click "up",cannot click "stop" to check PPC register

2) p2020 is at the status of "asleep",it cannot go to the status of "ready". /HRESET pin drive by cpld , Meeting document requirements,but p2020 cannot boot from flash.

what can i do ? thanks very much!

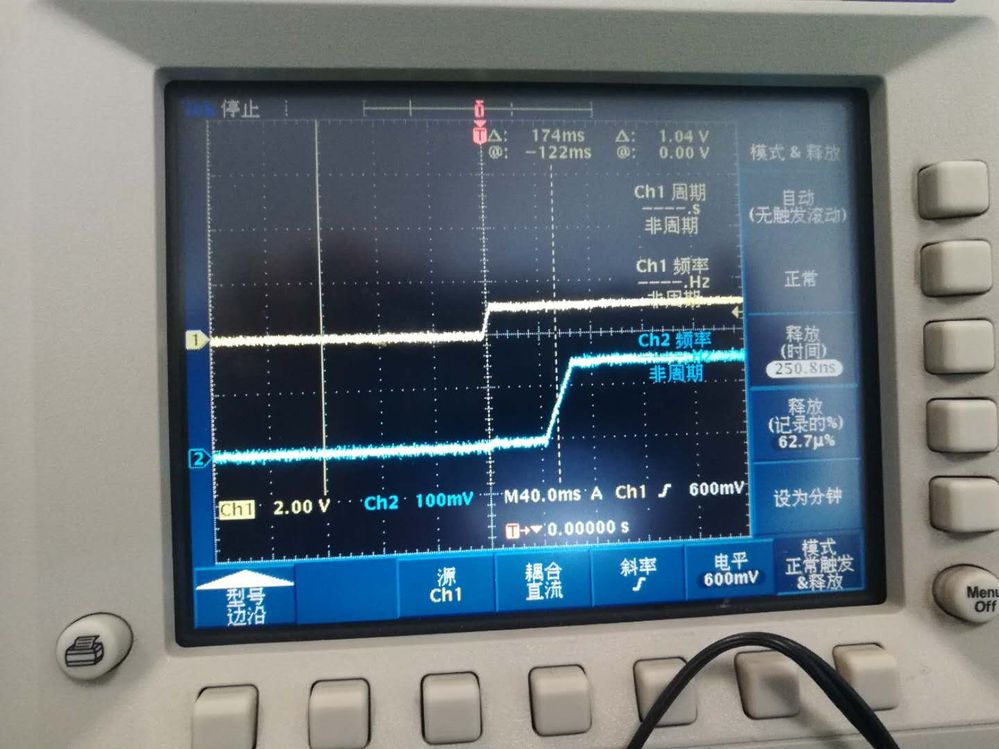

Yellow :1.05V core voltage blue:1.5Vvoltage

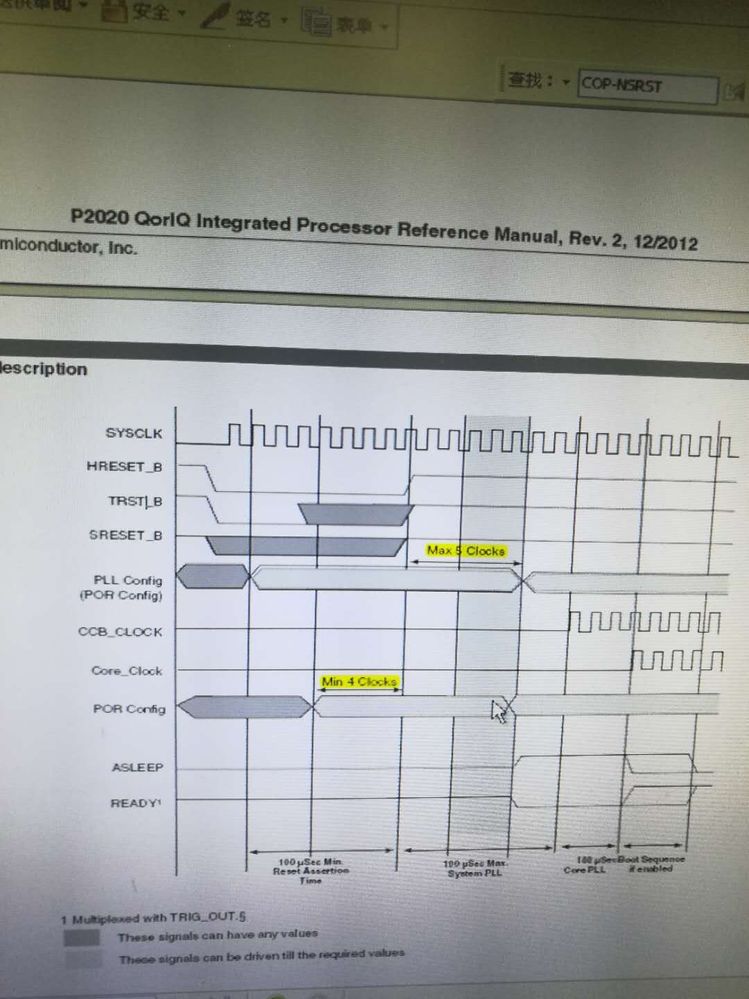

power on ,sysclk is 100MHz,HRESET_B meet this picture

ASLEEP pin is high , not go low...p2020 cannot boot

what can i do ?

Please look P2020 Reference Manual, Section 4.5.2 "Power-on reset sequence"

Before ASLEEP is negated (step 11 in this sequence), all previous steps should be passed successfully.

If you said HRESET is negated properly (step 4), than please check all steps after step 4. As far as I can see, you need to check if RCW loading procedure is finished properly, and RCW value is correct, and also please check if everything is correct with PCIe interface (proper clock is applied to serdes module), so it can finish PCIe training procedure successfully.

Have a great day,

Alexander

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------