- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Power Management

- :

- Power Management

- :

- Re: What does TPL stand for?

What does TPL stand for?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What does TPL stand for?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fabian,

TPL stands for transformer physical layer.

The MC33771/MC33772 (battery cell controller) and MC33664 (TPL transceiver) communication solution is based on a passive electrical bus (no repeater, no amplifier).

High-speed differential isolated communication is achieved through the use of transformers.

The benefits of such a solution are:

• more robust Electromagnetic Compatibility (EMC) characteristics (intrinsic transformer

common mode rejection)

• greater high-voltage isolation

• better communication speeds and synchronized measurements

• lower cost

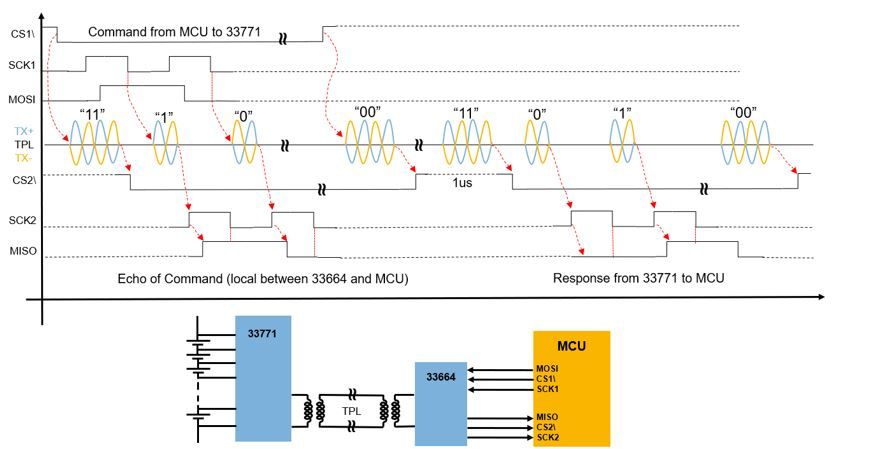

The picture below illustrates how the MC33664 TPL transceiver exchanges data between the MCU and the MC33771.

First, you can notice that the MCU needs two SPI ports for the SPI to TPL translation; one for MOSI and one for MISO. At the top of the waveforms, the MCU is going to initiate a command to the MC33771. CS1\ being asserted by the MCU causes a start of message double positive pulse on the TPL bus. This double pulse in turn causes CS2\ to be asserted on the MC33664. This starts the process of the command message from the MCU to be echoed back to the MCU on the MISO pin. After the start of message double pulse, data is clocked out of MOSI and translated onto the TPL bus. The signal on the TPL bus is a differential sine wave. The phase of the sine wave dictates whether it is a one or a zero. After the MOSI data is completed, CS1\ is de-asserted by the MCU and this causes an end of message double negative pulse. After the MC33771 processes the command, it then initates putting it is response data on the TPL bus. The reverse process occurs where the start of message double pulse on the TPL bus is translated to by the MC33664 and it asserts the CS2\ pin on the MCU so it can now receive data on MISO.

I hope it clarifies your question. Let us know if you need any further information.

Best regards,

Tomas

PS: If this answer helps to solve your question, please mark it as "Correct" or “Helpful”. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @TomasVaverka,

is this also described in any data sheet that the MC33664 generates an echo?

BR, Patrick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Tomas

but ,33771 is slave , reponse sclk was generated by 33771?

Regards

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,Tomas

TPL transceiver look like CAN FD protocol? Is there bit time ? is there a sample point ? what's the speed?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Thomas,

thanks for the fast and detailed response. Your answer is very helpful. Thanks!

Best regards,

Fabian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content