- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- Pシリーズ

- :

- p1012: GPIO: What does RISC_ GPIO[x] mean in the "QUICC Engine Multiplex Options" table?

p1012: GPIO: What does RISC_ GPIO[x] mean in the "QUICC Engine Multiplex Options" table?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

p1012: GPIO: What does RISC_ GPIO[x] mean in the "QUICC Engine Multiplex Options" table?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

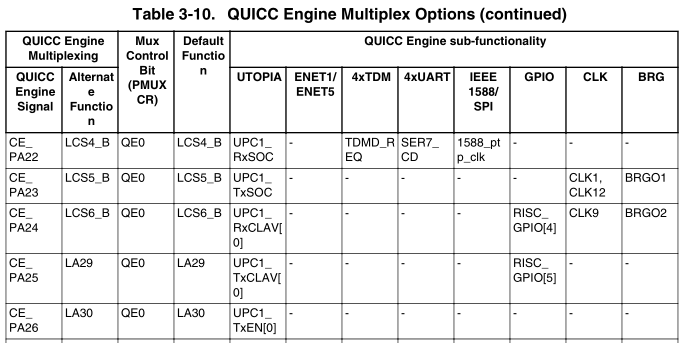

What does RISC_ GPIO[x] mean in the "QUICC Engine Multiplex Options" table?

As the below table said, CE_PA24 has a sub-functionality named as RISC_CPIO[4]? what does it mean?

In the beginning, I think it means that CE_PA24 can be used as GPIO. But I also do a test by using CE_PA22,

although it does not have the GPIO sub-functionality, but it still can be used as GPIO, can output/input value.

So could you please help to clarify it?

Thank you,

Carl

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Pavel,

Thanks a lot for your clarification!

But I have a new question, as you said, prefixed with RISC_ means that the GPIO is belong to QE.

so, my question is that what is the different between QE GPIO and SOC GPIO, I found that both

these two kind of GPIO can be controlled by GUTS_DIR1n, GUTS_CPDATn, GUTS_CPPAR1n

register, so what is the character of QE GPIO?

Thank you,

Carl

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The RISC_GPIO means that these pins are controlled by RISC QE engine and GPIO interface from the P1012 core.

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The RISC_GPIO are the GPIOs those belong to Quicc Engine (QE). Since QE has a RISC (reduced instruction set computation) engine embedded inside so the to differentiate the QE's GPIOs from SoC GPIOs, the term RISC_ is prefixed for QE.

For example, RISC_GPIO[4] is multiplexed with CLK9 and BRGO2 on CE_PB24.

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------