- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- OSBDMとTBDML

- :

- Re: Verifying mc9s12xep768

Verifying mc9s12xep768

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Verifying mc9s12xep768

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have been able to use MemoryDump to read the p and d flash from chip mc9s12xep768 as detailed in this post:

It would be interesting if there was a debug version of MemoryDump to see what it is doing.

However I have not been successful verifying with HC12S.

There are a number of things I've noticed.

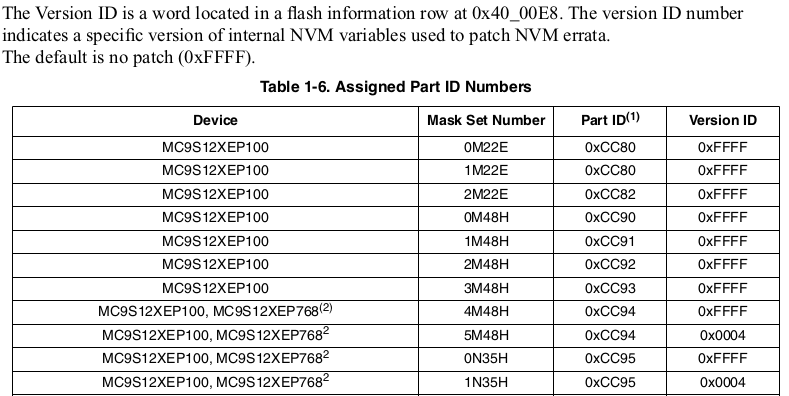

Firstly it detects cc92 as an id. but according to the table that is not right:

and in this post with a similar chip it was cc94

https://community.nxp.com/t5/OSBDM-and-TBDML/Erasing-and-Flashing-mc9s12xep768/m-p/1754397

If this was so then the way it tries to access might be different causing it to fail. Perhaps this information is in hcs12_devices.xml.

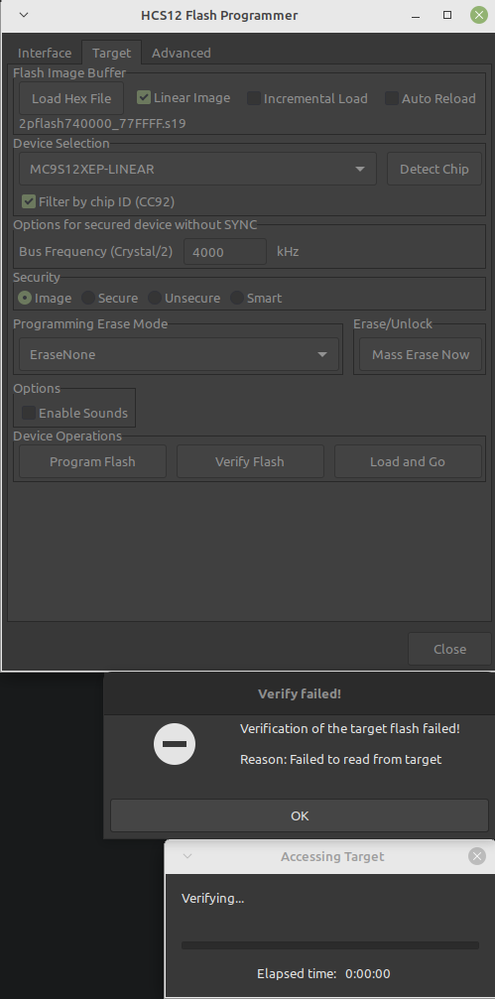

If I unselect what HC12S id chooses and use xep 100 then it starts to read but gives the following message:

Secondly I have checked and a ceramic resonator appears to provide an 8MHz clock which I measured rather approximately on an oscilloscope - so I wondered what is the rate at which the processor BDM communicates with the usbdm device? - it seems 250KHz according to MemoryDump. otherwise if it was 4MHz then maybe my Dupont type leads are not sufficient.

There is only a decoupling capacitor on the reset pin on examination no external watchdog.

This is the message I get when HC12S chooses the processor xep linear cc92

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

There is a debug version of Memory dump installed by the .deb.

The chip I have is a MC9S12XEP100 and identifies as CC94.

Note the info at the bottom of the table:

The last few bits are described as minor mask set revision and are ignored in the XML file (sdidMask).

Several SDID are treated as equivalent for MC9S12XEP100-family and MC9S12XEP-Linear:

<sdidMask value="0xFFF0" />

<sdid value="0xCC80" />

<sdid value="0xCC90" />

<sdid value="0xC480" />

<sdid value="0xC080" />

An 8MHz clock leads to an BDM interface frequency of 4MHz.

The Communication Speed selection in memory dump is not used for HCS12. It is there for some other targets.

Really clutching at straws here but how long is the ribbon cable on the BDM?

Check for noise on the power supply.

bye

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

the leads are 8", there does not seem to be any significant noise on the power supply at least that I saw on the oscilloscope.

I wonder if there is a way to test the actual usbdm device.

It was new and I did update the Firmware to 4.12.2. The Firmware verify is as follows:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Memory dump uses generic HCS12 code and does not use the device data at all really.

bye