- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- モデルベース・デザイン・ツールボックス(MBDT)

- :

- モデルベース・デザイン・ツールボックス(MBDT)

- :

- Re: SIL Testing Issue with NXP S32K3xx Hardware Board

SIL Testing Issue with NXP S32K3xx Hardware Board

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SIL Testing Issue with NXP S32K3xx Hardware Board

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

We are encountering an issue while attempting to create a SIL test harness for our model using the NXP S32K3xx hardware board. The error message "Error: The model is configured to create a SIL block, which is not supported for the selected hardware board. To resolve this, search for 'Create block' in the Configuration Parameters dialog box and set it to 'None' or 'PIL'" persists, even though the 'Create block' setting is already set to 'None'.

Model and Hardware Configuration Details:

- Hardware Board: NXP S32K3xx

Steps Taken to Troubleshoot:

- Verified 'Create Block' Setting: Double-checked the 'Configuration Parameters' dialog box to ensure that the 'Create block' setting is indeed set to 'None'.

Tried this but still getting the same error.

We have attached an image of configuration parameter of our model and the error message for your reference.

We kindly request your assistance in resolving this issue. Any guidance or suggestions would be greatly appreciated.

Thank you for your time and support.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @db_1008

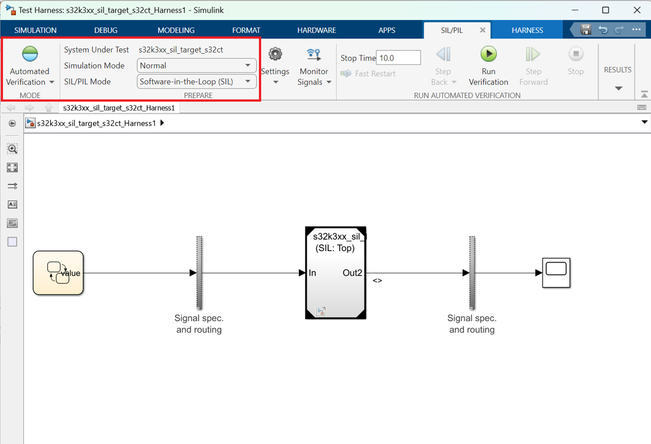

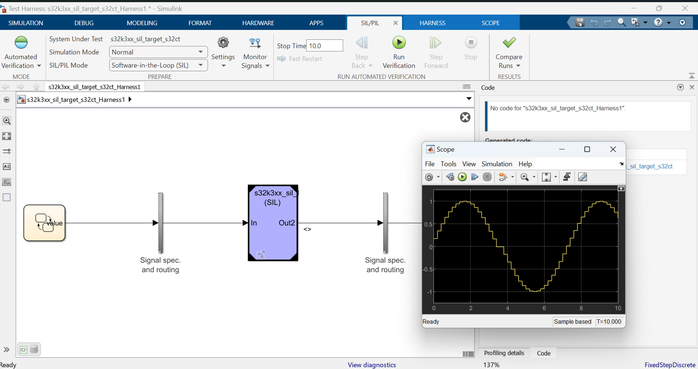

For trying to investigate the issue you have encountered, I have performed the following steps:

1. Opened the s32k3xx_sil_target_s32ct.slx file, delivered with the toolbox inside the following folder - {toolbox_installation_path}/S32K3_Examples/sil/s32k3xx_simple_s32ct

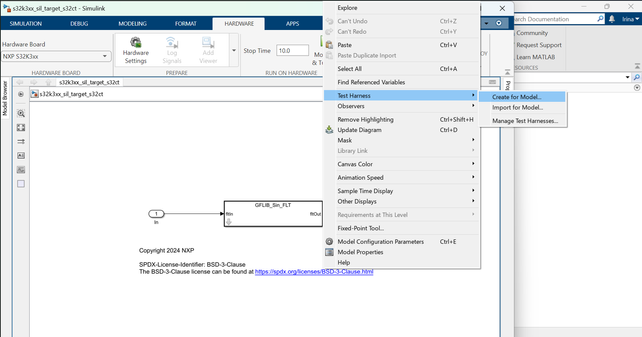

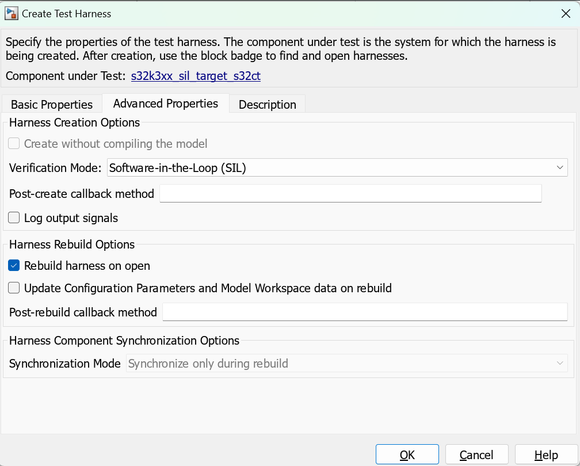

2. Right clicked the Simulink model canvas and chose Test Harness - Create for Model. In the opened Create Test Harness tab I have completed the Advanced Properties tab with the same settings as the ones you attached inside the SIL_Harness_Creation.png

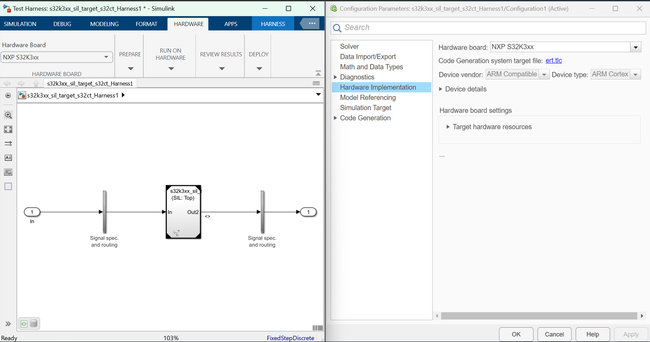

3. When opening the harness model, and inspecting its properties, I am noticing that the model is created being set for the NXP S32K3xx.

4. Added inputs and outputs inside the harness for performing a SIL simulation

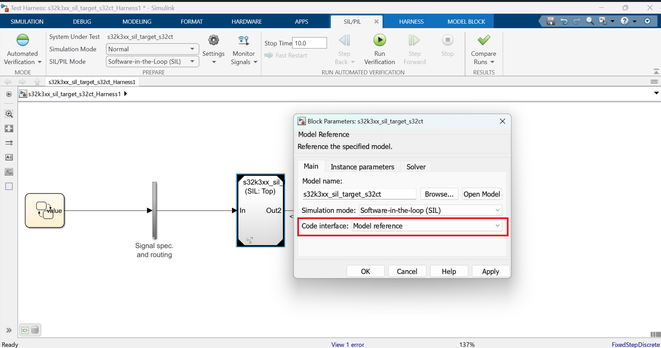

5. Set the Code Interface as Model Reference for the SIL block inside the harness model

6. From the SIL/PIL tab, I am able to successfully run an Automated Verification

Could you please let us know if this is the use case that you are trying to achieve, and check if these steps also work on your setup?

In case you are still encountering issues, could you also please help us with more details so that we could troubleshoot the problem? It would help us to know:

1. Is the model for which you are creating a harness already configured for an S32K3 hardware board?

2. What version of MBDT for S32K3 and MATLAB are you using?

Thank you,

Irina

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @Irina_Costachescu

We are following the same above mentioned steps. but getting an error while creating test harness. please find attachment image of the error as well as the model zip file.

the model for which we are creating a harness already configured for an S32K3 hardware board.

The version are :

Matlab Version = R2023b

NXP Toolbox version = Model-Based Design Toolbox for S32K3xx Series Version 1.5.0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @Abhijeet-Starkenn

I have taken a look and tried to create test harnesses for the model attached, and by following the steps mentioned in the previous reply, I was not able to reproduce this error.

However, I have managed to reproduce it by trying to create a Test Harness for the Subsystem placed in your model, instead of creating it for the model itself.

While we furtherly investigate the possibility of creating Test Harnesses for subsystems inside a model, would it be a suitable approach for you to create the Test Harness for the model itself?

Could you please provide more details on the use case that you are trying to achieve so that we could provide more tailored guidance?

For following this proposed workaround (create the Harness for the model), right click on the model canvas and choose Test Harness - Create for Model, as it is described in the Step 2 of the previous reply I have added to this thread.

Please let us know your thoughts on this,

Irina

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Could you please proceed with setting

Test Harness -> Create for subsystem -> Advanced properties ->

Verification Mode: Software-in-loop -> Ok.

After this steps, on my system i am getting error "Harness creation Aborted" with error "Error: The model is configured to create a SIL block, which is not supported for the selected hardware board. To resolve this, search for 'Create block' in the Configuration Parameters dialog box and set it to 'None' or 'PIL'."

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

As mentioned in my previous reply:

I have managed to create a Test Harness by right clicking on the model canvas and choosing Test Harness - Create for Model, instead of Create for Subsystem.

Could you please provide more details on the use case that you are trying to achieve so that we could provide more tailored guidance?

Do you need specifically to create harnesses for subsystems, or is this proposed approach (creating the harness for the model itself) helping you in your use case?

Thank you,

Irina

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Any help on this?