- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 基于模型的设计工具箱(MBDT)

- :

- 基于模型的设计工具箱(MBDT)

- :

- 3-phase Inverter Emulation

3-phase Inverter Emulation

3-phase Inverter Emulation

Hello,

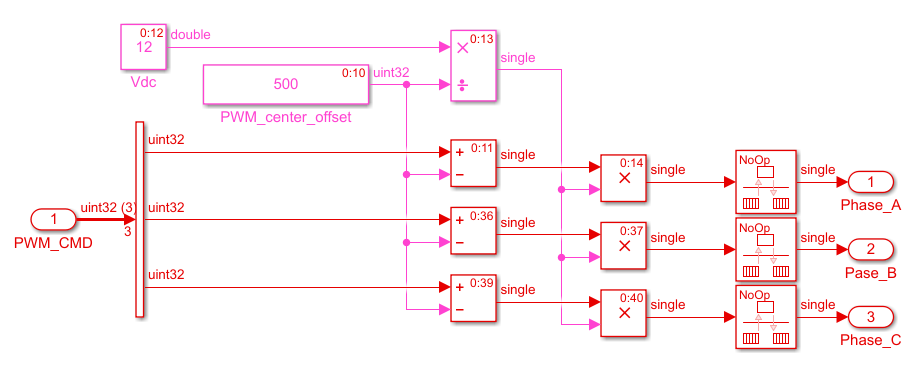

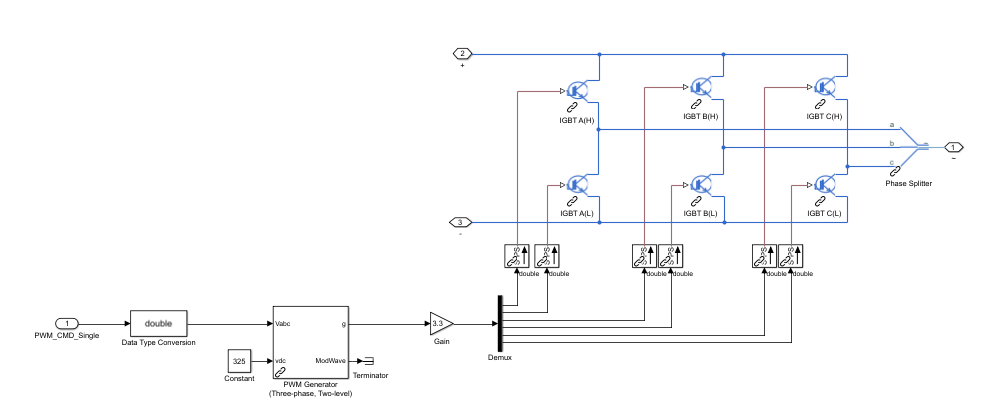

in PMSM Module 5: V/F Scalar Control this Subsystem is used to emulate the 3-phase driver:

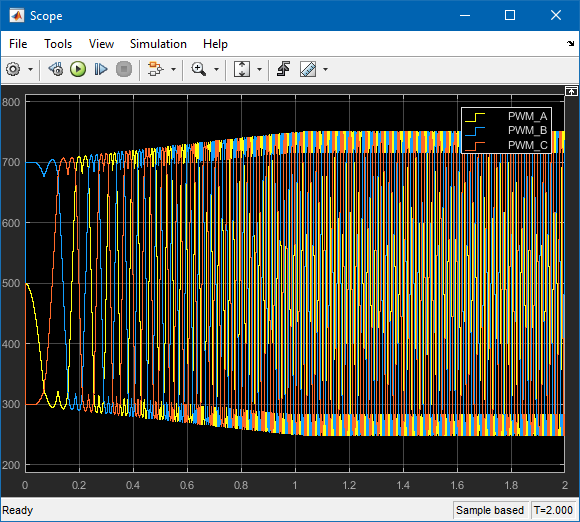

PWM_CMD looks like this, so the original is multiplied by 1000 and duty cycle is always between 0 and 100% (e.g. PWM_B at the beginning 700 = 70%):

If I'm right this means at the beginning the high side igbt PWM_B(H) = 70% and low side igbt PWM_B(L) = 30% ??

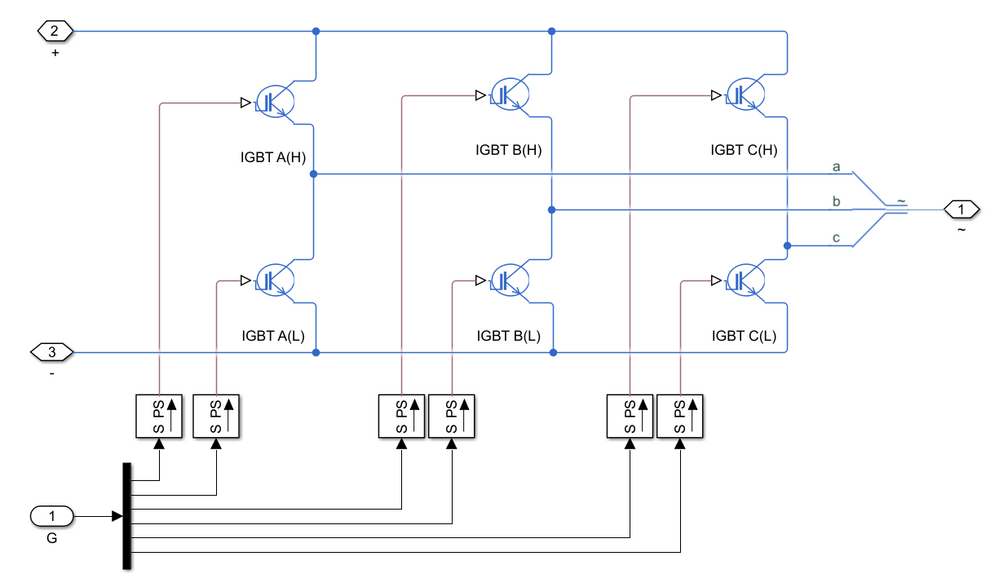

Now I want to simulate the inverter like this:

For this I have to get the Gate Signals called "G" but I don't know them.

How could I get them from the duty cycle above ?

The Inverter is working in complementary mode, so every time IGBT A(H) is on IGBT A(L) has to be off.

V IN(ON) Threshold = 2.6V, so the gates are driven by 3.3V directly by the controller.

Best regards

Leon

Hi Leon,

If I'm right this means at the beginning the high side igbt PWM_B(H) = 70% and low side igbt PWM_B(L) = 30% ?

You are correct!

For this I have to get the Gate Signals called "G" but I don't know them.

How could I get them from the duty cycle above ?

You take the PWM duty cycle computed by the SVM (which is between 0 and 1 - you do not need to scale it up to 100% or 1000% since you do not use the hardware) and you transform the value of the duty factor into 2 booleans based on a simple comparison.

I do not know how exactly you are simulation the inverter (powersim or something else) but you need to have the model execution time smaller than the time allocated for PWM computations.

For example: if the FAST LOOP is 100usec (you compute a duty cycle at each 100usec) then if you wish to have a gate command resolution of 1% then you need to simulate the inverter subsystem 100 times faster than the subsystem that computes the duty cycles.

e.g. if you wish to have 70% ON for IGBT A(H) then you keep G A(H) ON for 70 cycles and then you switch it OFF and do the opposite for the lower part.

In theory - the inverter and motor shall be simulated with the smallest step possible in order to replicate the continuous time domain. In this case you need to have the inverter and motor simulated @ 1e-6seconds (might be over-killing for a PC)

Hope this helps!

Daniel

Hello dumitru-daniel.popa

You take the PWM duty cycle computed by the SVM (which is between 0 and 1 - you do not need to scale it up to 100% or 1000% since you do not use the hardware) and you transform the value of the duty factor into 2 booleans based on a simple comparison.

Okay I understand this for principle.

I have the three PWM signals which are between 0 and 1

But how to compute the comparision so that PWM_A = Logical 1 (in simscape the gate signal has to be 3,3) for 70 cycles in your example ?

I do not know how exactly you are simulation the inverter (powersim or something else) but you need to have the model execution time smaller than the time allocated for PWM computations.

I'm using the Simscape Power Systems Toolbox for the Inverter and PMSM machine. The IGBT is in the "Semiconductors" Library.

Best regards

Leon

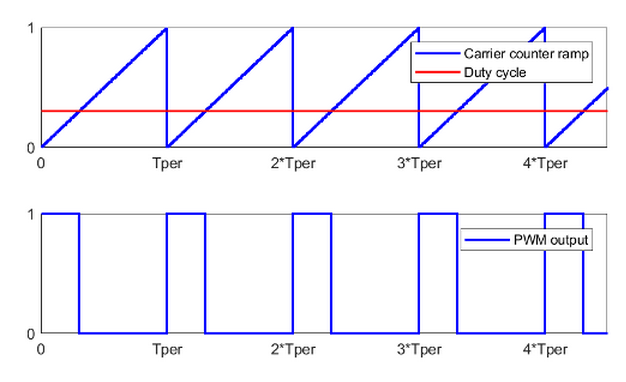

Okay I found a block "PWM Generator" which you can use to generate the gate signals.

It is working like this:

So the Inverter model now looks like this.

But now the required time for the Simulation veeeery long...

Best regards

Leon