- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Interfacing MPC5566 with External Memory

Interfacing MPC5566 with External Memory

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to interface external memory with MPC5566. The program works fine with the external debugger attached but crashes when attempting to boot from internal flash in release mode. Based on some research, it seems that since the debugger uses some scripts to initialize MMU and other registers while bypassing BAM, the code works fine. There are some posts which suggest that similar initialization needs to be manually done when booting from internal flash. However, I am not able to identify all the changes that need to be made and which files need to be modified for the same. Some code pertaining to MPC5566DEMO_AXM_0321 is not executed (since this board is not used) in the following functions:

__initEBIChipSelects

__initMMUExternalMemory

I have tried to add some code based on that provided for MPC5566DEMO_AXM_0321 replacing values with those specified in the debug script but with no success.

Any help in this regard would be sincerely appreciated. It would be great if some links or sample code is provided for step-by-step interfacing with external memory.

Thanks in advance.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

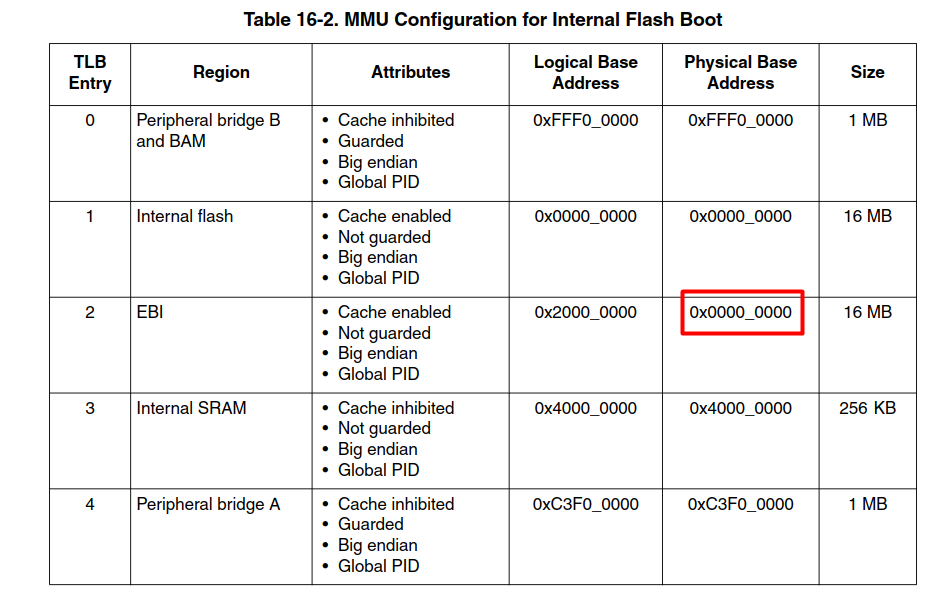

Default MMU TLB entry setting for EBI space is set with Physical Base Address 0x0000_0000. It is because of possible boot from external bus. This need to changed to 0x2000_0000 by user code (it is also being set by debugger script what can be enough in case RAM target, but not in case internal FLASH target because in this case debugger script executes before execution of BAM code).

It can be changed by following source code for instance:

static asm void External_SRAM_MMU_init(void)

{

nofralloc

lis r3, 0x1002 /* Select TLB entry #, define R/W replacment control */

mtMAS0 r3 /* Load MAS0 with 0x1002 0000 for TLB entry #2 */

tlbre /* Get TLB entry # information */

mfspr r3, MAS3

oris r3, r3, 0x2000 /* EBI Physical Base Addr changed to 0x2000_0000 */

ori r3, r3, 0x0000

mtMAS3 r3

msync /* make sure we finished all memory accesses */

tlbwe /* Write entry defined in MAS0 (entry 1 here) to MMU TLB */

isync /* Wait for tlbwe to complete, then flush instruction buffer */

blr

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Default MMU TLB entry setting for EBI space is set with Physical Base Address 0x0000_0000. It is because of possible boot from external bus. This need to changed to 0x2000_0000 by user code (it is also being set by debugger script what can be enough in case RAM target, but not in case internal FLASH target because in this case debugger script executes before execution of BAM code).

It can be changed by following source code for instance:

static asm void External_SRAM_MMU_init(void)

{

nofralloc

lis r3, 0x1002 /* Select TLB entry #, define R/W replacment control */

mtMAS0 r3 /* Load MAS0 with 0x1002 0000 for TLB entry #2 */

tlbre /* Get TLB entry # information */

mfspr r3, MAS3

oris r3, r3, 0x2000 /* EBI Physical Base Addr changed to 0x2000_0000 */

ori r3, r3, 0x0000

mtMAS3 r3

msync /* make sure we finished all memory accesses */

tlbwe /* Write entry defined in MAS0 (entry 1 here) to MMU TLB */

isync /* Wait for tlbwe to complete, then flush instruction buffer */

blr

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Thank you very much for your response. I was able to get the code working by adding and invoking the above mentioned function. I have been struggling with this issue for days. Very grateful for the help. Thanks again.