- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Initialize peripherals on core1

Hi,

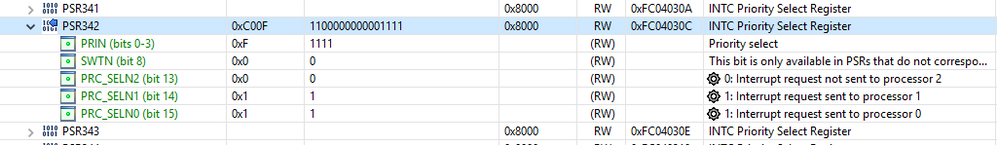

I'm using 2 cores (both z4) of the MPC, where each core uses some peripherals. However all interrupt vectors are configured to be executed on core1. When I initialize for example the SPI5 peripheral on core1, the PSR342 shows that the interrupt is sent to both cores. During initialization the default (core0 target) bit is not cleared, only the core1 target is added.

What is the recommended way to prevent this? I know I can remove the core0 target manually, but maybe there is a nicer solution? I'm using SDK RTM 2.0.0

Hello,

The INTC peripheral is designed to work like this: the reset value of the INTC_PSRn->PRC_SELN0 bitfield is 1, so all interrupts are enabled for core0 by default. Unfortunately, in SDK PA RTM 2.0.0 there is no way to automatically prevent this. You can only manually disable the interrupt for core0 before enabling the peripheral. This behavior is shown in the interrupt_control_multicore example.

However, the interrupt_manager driver has been recently rewritten and this issue is no longer present. When calling INT_SYS_EnableIRQ(irqNum), the driver will enable irqNum only for the current core and disable it for other cores. This feature should be included in the future SDK PA releases.

Best wishes,

Mihai Volmer