- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- MCUXpresso IDE

- :

- Re: Stack pointer in wrong memory

Stack pointer in wrong memory

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Stack pointer in wrong memory

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I'm having trouble trying to get the stack pointer to be where I want it using MCUExpresso with the imxrt1052.

I'm using version 10.2.1 of the IDE and version 2.5.0 of the EVKB-IMXRT1050 SDK.

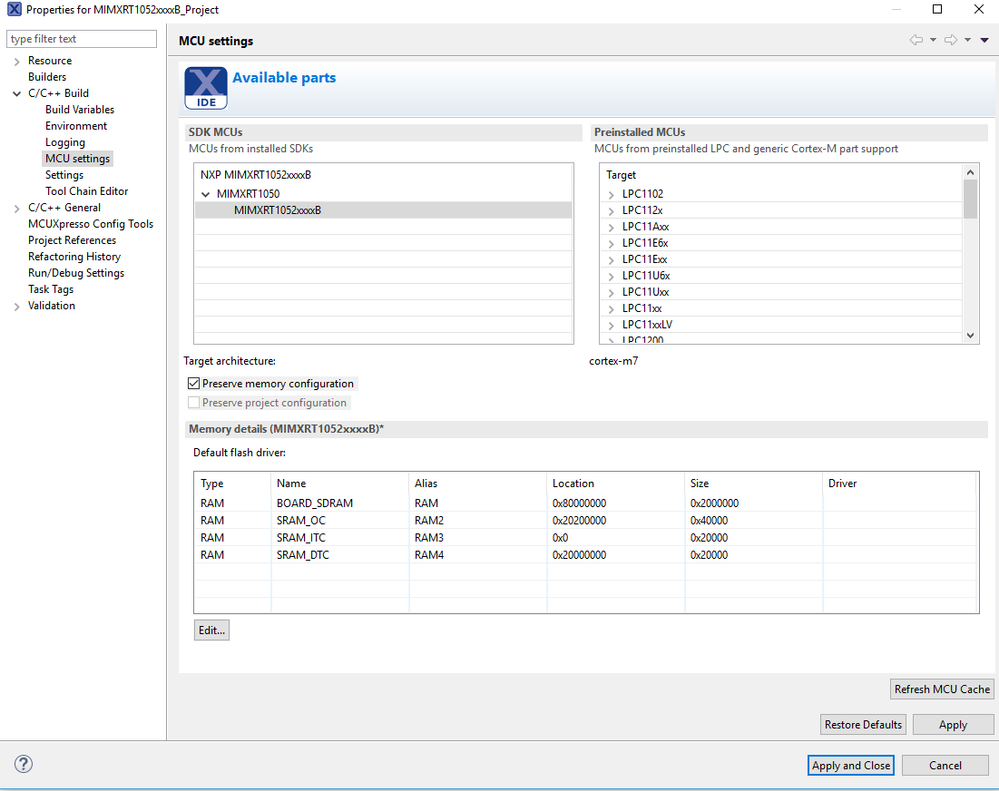

My memory is configured thus which is pretty standard:

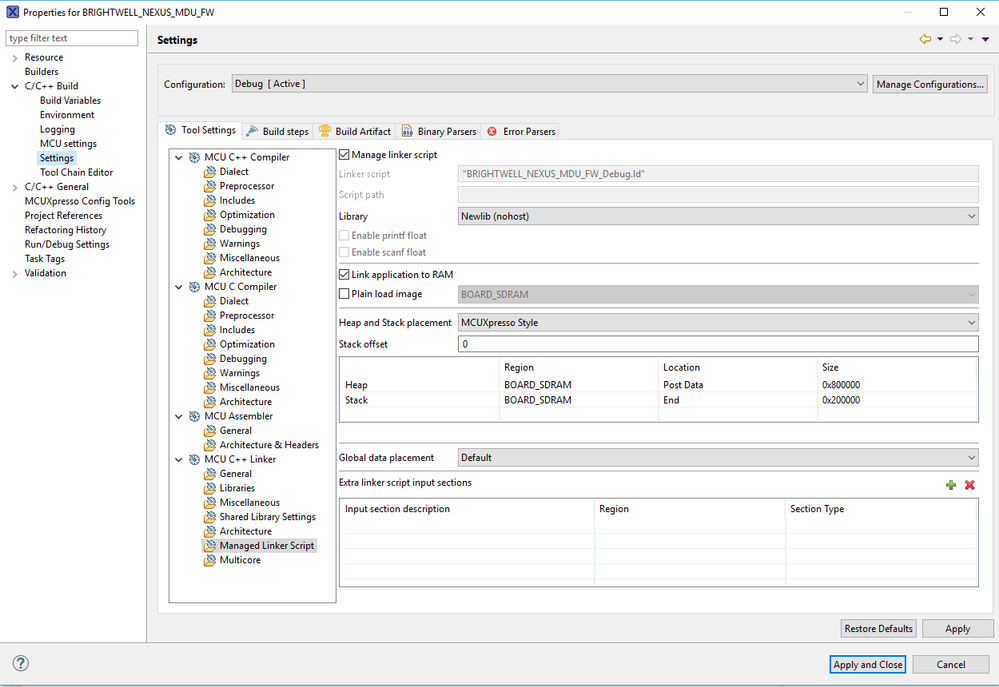

And I've configured the linker to link the application to RAM and to set the heap and stack to SDRAM as shown below:

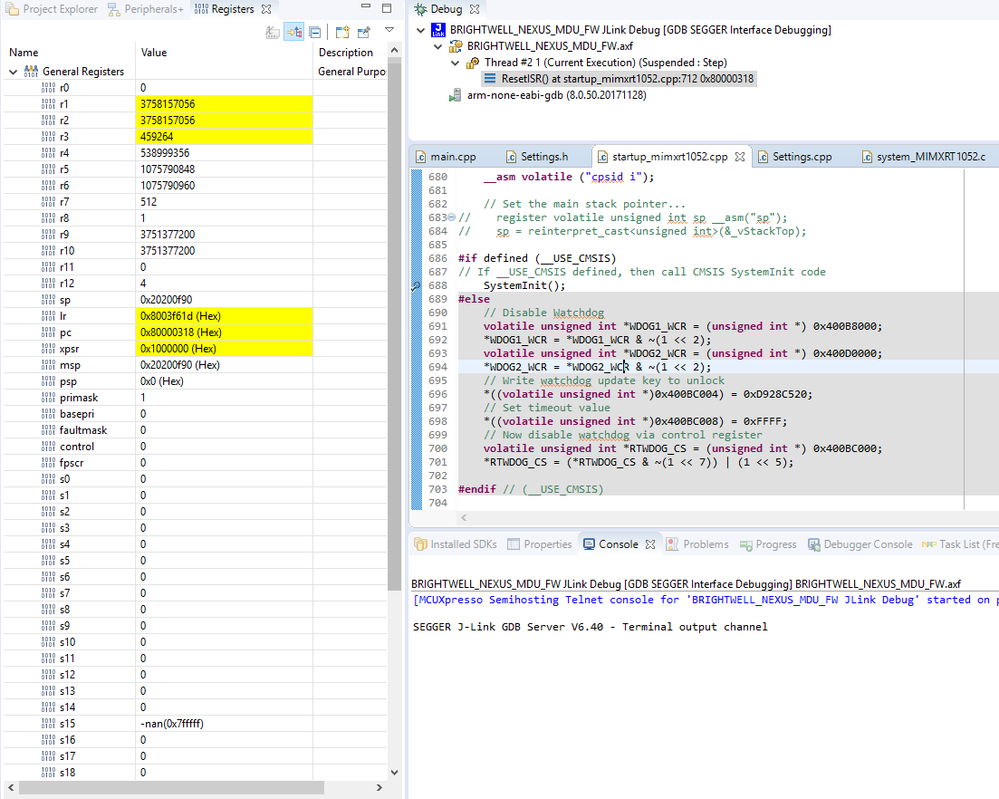

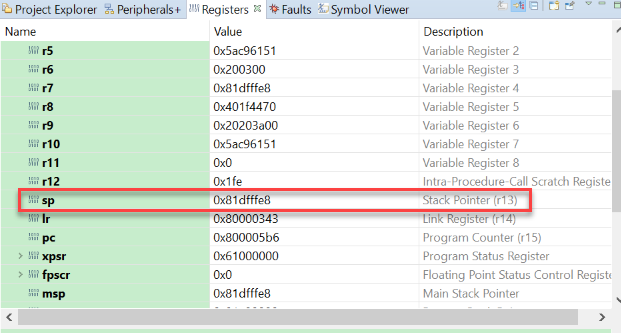

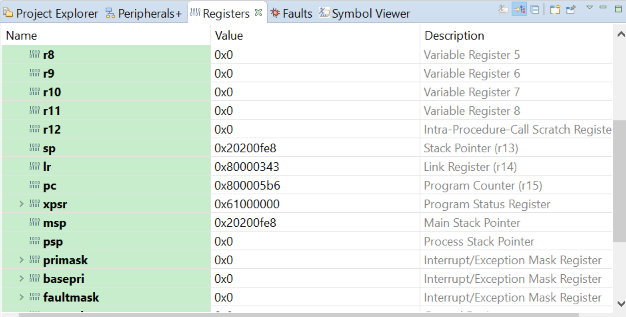

However when I set a breakpoint in the ResetISR function the stack pointer (r13) is always in the internal SRAM_OC area:

The linker map file shows exactly what I expect it to show as shown here:

/* Reserve and place Heap within memory map */

_HeapSize = 0x800000;

.heap : ALIGN(4)

{

_pvHeapStart = .;

. += _HeapSize;

. = ALIGN(4);

_pvHeapLimit = .;

} > BOARD_SDRAM

_StackSize = 0x200000;

/* Reserve space in memory for Stack */

.heap2stackfill :

{

. += _StackSize;

} > BOARD_SDRAM

/* Locate actual Stack in memory map */

.stack ORIGIN(BOARD_SDRAM) + LENGTH(BOARD_SDRAM) - _StackSize - 0: ALIGN(4)

{

_vStackBase = .;

. = ALIGN(4);

_vStackTop = . + _StackSize;

} > BOARD_SDRAM

I've tried cleaning the build and also creating a small application with no frills straight from the SDK and that doesn't help. I've also tried removing the BOARD_FLASH memory and also the internal SRAMs so that I only have SDRAM and that makes no difference.

If you look carefully at the code snippet in the last pic you can see where I've commented out manually setting the sp using the _vStackTop value set by the linker. This kinda does work in that the stack pointer gets set properly, but I find that the application dies after a while due to stack corruption of a C++ object that was created on the stack within main.

Any ideas?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Gary,

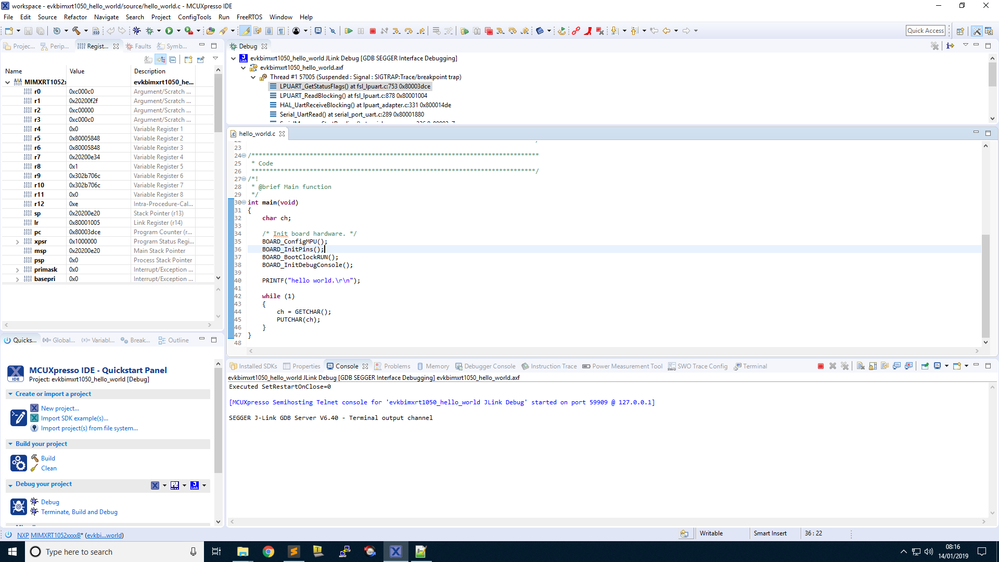

The issue you are seeing is a consequence of debugging a RAM based image with SEGGER and is described correctly by SEGGER in that their debug environment does not set the initial stack pointer based on the image - instead it is inherited from the previous application (likely the bootROM).

In contrast a LinkServer/CMSIS-DAP debug (the default if using the OpenSDA debug probe) will identify that you are debugging from RAM and setup the stack based on the setting in the image - e.g. see text snip from a LinkServer debug log below:

Starting execution using soft reset with PC 0x200002F1 SP 0x20020000 from load at 0x20000000

Note: in this example, the SP is set to the top of the first RAM bank i.e. the top of the D_TCM in this case.

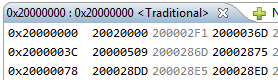

If you look at the binary values at the start of the image in RAM, you will see the linker has correctly inserted the SP value (first entry) based on the managed linkerscript settings and also the entry point for the image:

If an image is run using an actual reset (e.g. from Flash) then the bootROM would mimic the cortex hardware setup and set the stack based on the image.

I hope this helps,

Yours,

MCUXpresso IDE Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I don't have access to a board or J-Link to check this right now, but I suspect that it could actually be the debug probe that is setting the SP in the background.

Can you post the text from the debug messages log in the Console View after you hit the breakpoint you have set in ResetISR() ?

Regards,

MCUXpresso IDE Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hiya

Ok that sounds plausible. Doesn't look like anything except reads here, but here you go (breakpoint was on main this time not the ResetISR)...

I have been looking at the start-up code that is presumably produced by the SDK for the actual board and I can't see where the actual SP is set anyway. There's an array called g_pfnVectors that is copied to the vector table offset register. The first element of this array is what the stack pointer should be set to (and I've checked this is correct), but nothing is being done with this value?

[14-1-2019 01:49:16] Executing Server: "C:\Program Files (x86)\SEGGER\JLink_V640\JLinkGDBServerCL.exe" -nosilent -swoport 2332 -select USB=260108640 -jlinkscriptfile C:\Projects\Nexus\Software\Source\Workspace\BRIGHTWELL_NEXUS_MDU_FW\scripts\evkbimxrt1050_sdram_init.jlinkscript -telnetport 2333 -singlerun -endian little -noir -speed auto -port 2331 -vd -device MCIMXRT1052 -if SWD -halt -reportuseraction

SEGGER J-Link GDB Server V6.40 Command Line Version

JLinkARM.dll V6.40 (DLL compiled Oct 26 2018 15:06:02)

Command line: -nosilent -swoport 2332 -select USB=260108640 -jlinkscriptfile C:\Projects\Nexus\Software\Source\Workspace\BRIGHTWELL_NEXUS_MDU_FW\scripts\evkbimxrt1050_sdram_init.jlinkscript -telnetport 2333 -singlerun -endian little -noir -speed auto -port 2331 -vd -device MCIMXRT1052 -if SWD -halt -reportuseraction

-----GDB Server start settings-----

GDBInit file: none

GDB Server Listening port: 2331

SWO raw output listening port: 2332

Terminal I/O port: 2333

Accept remote connection: localhost only

Generate logfile: off

Verify download: on

Init regs on start: off

Silent mode: off

Single run mode: on

Target connection timeout: 0 ms

------J-Link related settings------

J-Link Host interface: USB

J-Link script: C:\Projects\Nexus\Software\Source\Workspace\BRIGHTWELL_NEXUS_MDU_FW\scripts\evkbimxrt1050_sdram_init.jlinkscript

J-Link settings file: none

------Target related settings------

Target device: MCIMXRT1052

Target interface: SWD

Target interface speed: auto

Target endian: little

Connecting to J-Link...

$$UserActionStart$$: Terms of use

$$UserActionEnd$$: Terms of use

J-Link is connected.

Device "MCIMXRT1052" selected.

Firmware: J-Link V10 compiled Oct 26 2018 12:04:17

Hardware: V10.10

S/N: 260108640

OEM: SEGGER-EDU

Feature(s): FlashBP, GDB

Checking target voltage...

Target voltage: 3.27 V

Listening on TCP/IP port 2331

Connecting to target...Executing J-Link script file function: ConfigTargetSettings()

Config JTAG Speed to 4000kHz

Found SW-DP with ID 0x0BD11477

Scanning AP map to find all available APs

AP[1]: Stopped AP scan as end of AP map has been reached

AP[0]: AHB-AP (IDR: 0x04770041)

Iterating through AP map to find AHB-AP to use

AP[0]: Core found

AP[0]: AHB-AP ROM base: 0xE00FD000

CPUID register: 0x411FC271. Implementer code: 0x41 (ARM)

Found Cortex-M7 r1p1, Little endian.

FPUnit: 8 code (BP) slots and 0 literal slots

CoreSight components:

ROMTbl[0] @ E00FD000

ROMTbl[0][0]: E00FE000, CID: B105100D, PID: 000BB4C8 ROM Table

ROMTbl[1] @ E00FE000

ROMTbl[1][0]: E00FF000, CID: B105100D, PID: 000BB4C7 ROM Table

ROMTbl[2] @ E00FF000

ROMTbl[2][0]: E000E000, CID: B105E00D, PID: 000BB00C SCS-M7

ROMTbl[2][1]: E0001000, CID: B105E00D, PID: 000BB002 DWT

ROMTbl[2][2]: E0002000, CID: B105E00D, PID: 000BB00E FPB-M7

ROMTbl[2][3]: E0000000, CID: B105E00D, PID: 000BB001 ITM

ROMTbl[1][1]: E0041000, CID: B105900D, PID: 001BB975 ETM-M7

ROMTbl[1][2]: E0042000, CID: B105900D, PID: 004BB906 CTI

ROMTbl[0][1]: E0040000, CID: B105900D, PID: 000BB9A9 TPIU-M7

ROMTbl[0][2]: E0043000, CID: B105F00D, PID: 001BB101 TSG

Cache: Separate I- and D-cache.

I-Cache L1: 32 KB, 512 Sets, 32 Bytes/Line, 2-Way

D-Cache L1: 32 KB, 256 Sets, 32 Bytes/Line, 4-Way

Enabling i.MXRT SDRAM

DCDC trim value loaded.

Clock Init Done

SDRAM Init Done

Executing J-Link script file function: ConfigTargetSettings()

Config JTAG Speed to 4000kHz

Found SW-DP with ID 0x0BD11477

AP map detection skipped. Manually configured AP map found.

AP[0]: AHB-AP (IDR: Not set)

AP[0]: Core found

AP[0]: AHB-AP ROM base: 0xE00FD000

CPUID register: 0x411FC271. Implementer code: 0x41 (ARM)

Found Cortex-M7 r1p1, Little endian.

FPUnit: 8 code (BP) slots and 0 literal slots

CoreSight components:

ROMTbl[0] @ E00FD000

ROMTbl[0][0]: E00FE000, CID: B105100D, PID: 000BB4C8 ROM Table

ROMTbl[1] @ E00FE000

ROMTbl[1][0]: E00FF000, CID: B105100D, PID: 000BB4C7 ROM Table

ROMTbl[2] @ E00FF000

ROMTbl[2][0]: E000E000, CID: B105E00D, PID: 000BB00C SCS-M7

ROMTbl[2][1]: E0001000, CID: B105E00D, PID: 000BB002 DWT

ROMTbl[2][2]: E0002000, CID: B105E00D, PID: 000BB00E FPB-M7

ROMTbl[2][3]: E0000000, CID: B105E00D, PID: 000BB001 ITM

ROMTbl[1][1]: E0041000, CID: B105900D, PID: 001BB975 ETM-M7

ROMTbl[1][2]: E0042000, CID: B105900D, PID: 004BB906 CTI

ROMTbl[0][1]: E0040000, CID: B105900D, PID: 000BB9A9 TPIU-M7

ROMTbl[0][2]: E0043000, CID: B105F00D, PID: 001BB101 TSG

Cache: Separate I- and D-cache.

I-Cache L1: 32 KB, 512 Sets, 32 Bytes/Line, 2-Way

D-Cache L1: 32 KB, 256 Sets, 32 Bytes/Line, 4-Way

Enabling i.MXRT SDRAM

DCDC trim value loaded.

Clock Init Done

SDRAM Init Done

Connected to target

Waiting for GDB connection...Connected to 127.0.0.1

Reading all registers

Read 4 bytes @ address 0x0020C746 (Data = 0x6148F8D0)

Read 2 bytes @ address 0x0020C746 (Data = 0xF8D0)

Received monitor command: reset

Executing J-Link script file function: ResetTarget()

J-Link script: ResetTarget()

DP0: 0x0BD11477

DP1: 0xF0000040

AHB-AP0: 0x03000042

AHB-AP1: 0xE000EDF0

AHB-AP3: 0x00030003

AHB-AP3: 0x00030003

DCDC trim value loaded.

Clock Init Done

SDRAM Init Done

Resetting target

Downloading 16128 bytes @ address 0x80000000 - Verified OK

Downloading 6352 bytes @ address 0x80003F00 - Verified OK

Downloading 4 bytes @ address 0x800057D0 - Verified OK

Writing register (PC = 0x80000304)

Read 4 bytes @ address 0x80000304 (Data = 0xB672B510)

Reading all registers

Read 4 bytes @ address 0x80000304 (Data = 0xB672B510)

Reading 64 bytes @ address 0x80000540

Read 2 bytes @ address 0x80000552 (Data = 0xF001)

Received monitor command: semihosting enable

Semi-hosting enabled (Handle on BKPT)

Received monitor command: exec SetRestartOnClose=0

Executed SetRestartOnClose=0

Setting breakpoint @ address 0x80000552, Size = 2, BPHandle = 0x0001

Starting target CPU...

...Breakpoint reached @ address 0x80000552

Reading all registers

Removing breakpoint @ address 0x80000552, Size = 2

Read 4 bytes @ address 0x80000552 (Data = 0xFB19F001)

Reading register (MSP = 0x20200F60)

Reading register (PRIMASK = 0x 0)

Reading register (PSP = 0x 0)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

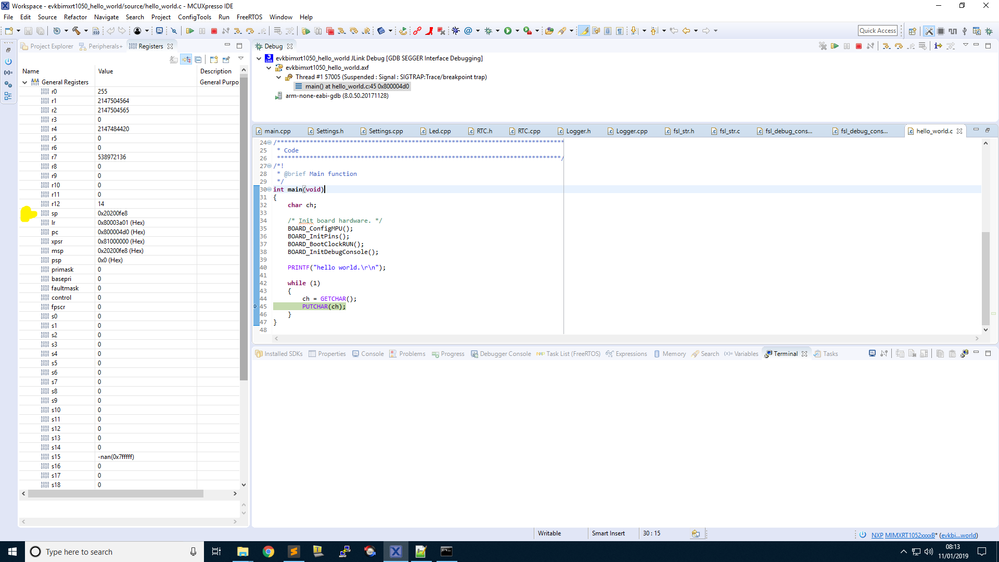

I would recommend customer to refer MCUXpresso SDK [hello world] project for MIMXRT1050-EVKB.

During SDK example project importing, please select [Link application to RAM].

Please refer the <evkbimxrt1050_hello_world_Debug.ld> file, I could check the heap and stack located at BOARD_SDRAM.

During debug, the stack pointer located at SDRAM memory:

I would recommend customer to update MCUXpresso IDE software.

Below is my MCUXpresso IDE software version info:

MCUXpresso IDE v10.3.0_prc3 [Build 2187] [2018-11-18]

Wish it helps.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Thanks for the reply. I did try that before but I did it again just to be sure. I imported the helloworld example from the latest SDK and made sure to select 'Link application to RAM' in the wizard. However it still shows the SP as being in the wrong place as shown in the follow screenshot...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Gary,

Could you update the MCUXpresso IDE to latest version V10.3?

Below is my MCUXpresso IDE version info:

MCUXpresso IDE v10.3.0_prc3 [Build 2187] [2018-11-18]

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I have tried installing version 10.3.0 and the problem is still there. I checked the release notes for 10.3.0 and it doesn't mention anything about this issue anyway.

I tried importing the helloworld demo that I had created in the previous version and that still showed the incorrect stack and so I completely deleted this project and created it new with the new IDE. This still shows the wrong stack:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

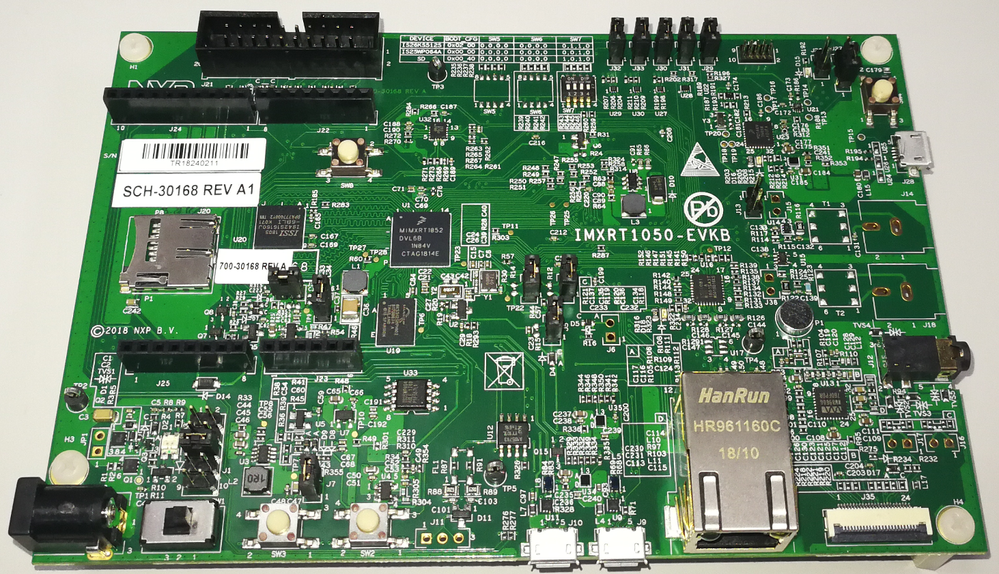

Could you check the board jumper setting?

BTW: The SW7 value is 0110.

During the debug, I am using on board OpenSDA.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hiya

Ok thanks I'll give that a try tomorrow as I'm not in the office today. Your board looks like an older revision as I think my SW7 is a DIP switch type and not jumpers. I used to have it set to 0001 for booting from Hyperflash but since I'm running from SDRAM, I've set it to 0000. I'll let you know how I get on.

I sometimes use the OpenSDA port for debugging but mostly use a Segger J-Link because our final product won't have OpenSDA so I need to get used to living without it.

Thanks.

Gary

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I can regenerate the issue with a standalone Segger J-Link Plus tool.

The stack point at 0x20200fe8.

I am checking with Segger about this issue.

I will let you know when there with any feedback.

Thanks for the patience.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Mike

Ok thanks, yes do let me know about the Segger issue. It will be annoying if that is the case as we already have an ongoing issue in that the Flash can't be mass erased using the JLINK debugger.

I'm currently trying to use OpenSDA for debugging but I've found it's not very reliable when configuring a project to run from external SDRAM. I have had it working in the past though so will keep on that. I have got to the point though where I can see that the MSP/SP are at definitely in SDRAM and with the value I'd expect. It's odd that the debug output from JLINK doesn't show that it is setting the stack pointer.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Gary,

Sorry for the later reply.

I got below feedback from Segger engineer:

best regards,

Mike

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike

OK thanks for passing that on. We'll leave our workaround in place that sets the stack pointer. For anyone else that needs this, here is what to do:

In the startup/startup_mimxrt1052.cpp file add the following two lines in the ResetISR function right after the asm instruction that disables interrupts:

__attribute__ ((section(".after_vectors.reset")))

void ResetISR(void) {

// Disable interrupts

__asm volatile ("cpsid i");

// Set the main stack pointer...

register volatile unsigned int sp __asm("sp");

sp = reinterpret_cast<unsigned int>(&_vStackTop);

If there is someone from NXP that produces the MIMXRT1050 SDK reading this, then please add this extra code to the startup file because without it, setting the stack to anything other than OCRAM in the IDE will be pointless because it will never get set. The OCRAM is quite small and for any sizeable project other than a simple 'hello world' I think you'd need to have the stack in external (SDRAM) memory.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Gary,

Thanks for the sharing.

best regards,

Mike