- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso Config Tools

- :

- Re: Are there bugs in ADC_ETC and ADC driver?

Are there bugs in ADC_ETC and ADC driver?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I found some points where I think that the MCUXpresso Config Tools v7 and the RT1020 Reference Manual are inconsistent.

*****

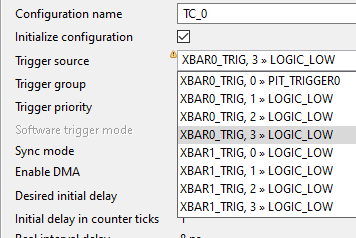

ADC_ETC SW and HW Trigger Mode

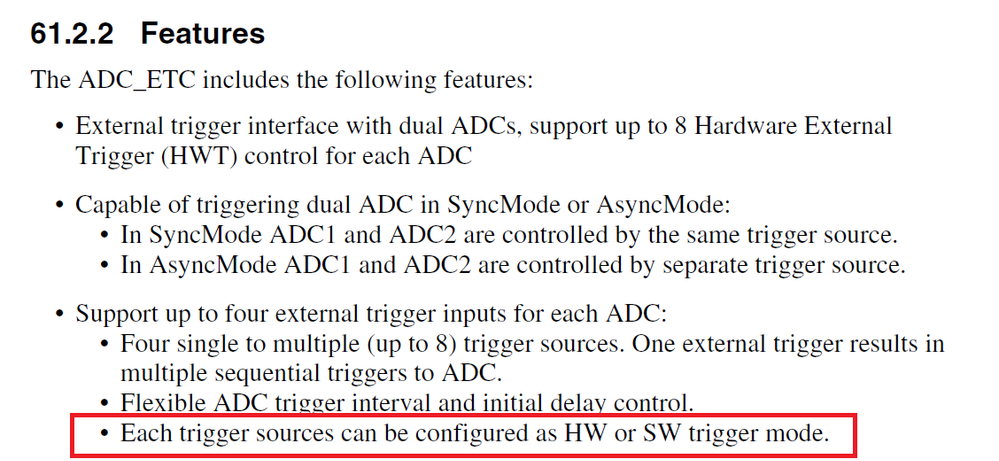

the reference manual of RT1020 states in the ADC-ETC Features list (61.2.2 in my version of the manual) that every trigger source can be configured as HW or SW trigger mode.

Additionally every TRIGx_CTRL register has the field TRIG_MODE which specifies HW or SW trigger mode.

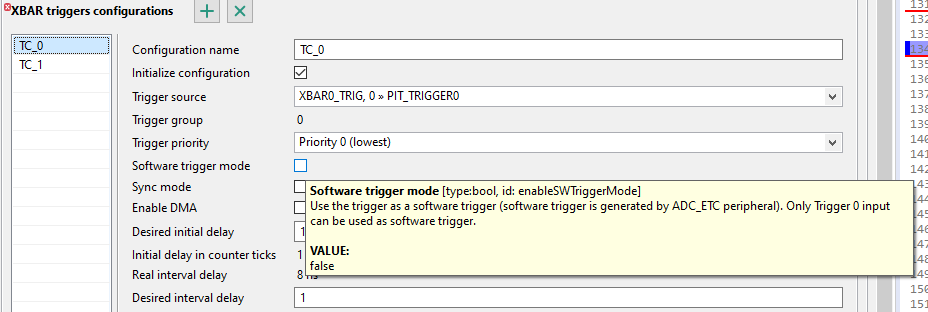

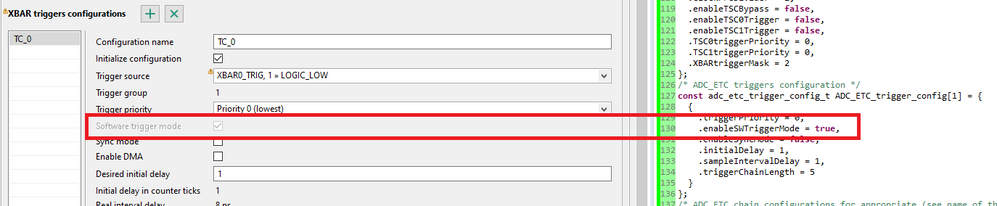

In MCUXpresso Config Tools v7 > peripheral tool the help text states that only Trigger 0 can be used as software trigger

If I select the Software trigger mode and then switch the Trigger source to XBAR0_Trig,1 the checkbox will be greyed out and I can not change the Software trigger mode but it will keep the setting for it (from the selection before switching to XBAR0_Trig,1). The setting will also be set in the generated source code.

Is the reference manual correct and every Trigger source can be used as Software Trigger or is the setting in MCUXpresso Config Tools correct and only XBAR0_TRIG 0 can be used as Software Trigger?

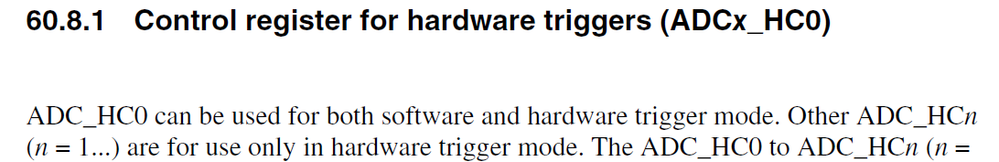

Maybe the incorrect information comes from the ADC peripheral where only the ADCx_HC0 register can be used as Software Trigger.

****

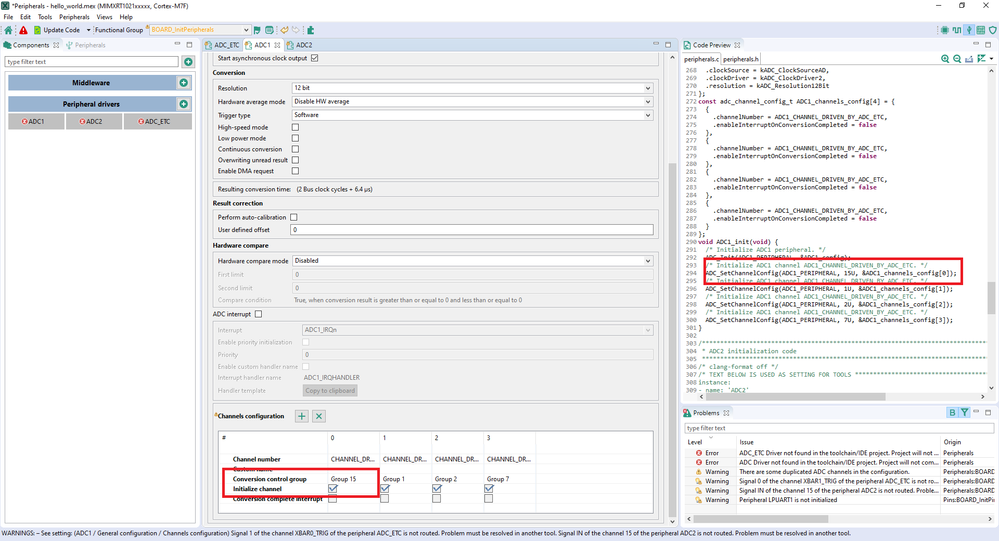

ADC_ETC and ADC peripheral Conversion control group

It is possible to select Group 0 to Group 15 in the ADC peripheral driver but the RT1020 only has 8 registers per ADC.

If I select the ADC1 peripheral driver and a Conversion control group 15 the generated code includes the line

ADC_SetChannelConfig(ADC1_PERIPHERAL, 15U, &ADC1_channels_config[0]);

and this method tests the second parameter with

assert(channelGroup < FSL_FEATURE_ADC_CONVERSION_CONTROL_COUNT);

where the macro is defined as

#define FSL_FEATURE_ADC_CONVERSION_CONTROL_COUNT (8)

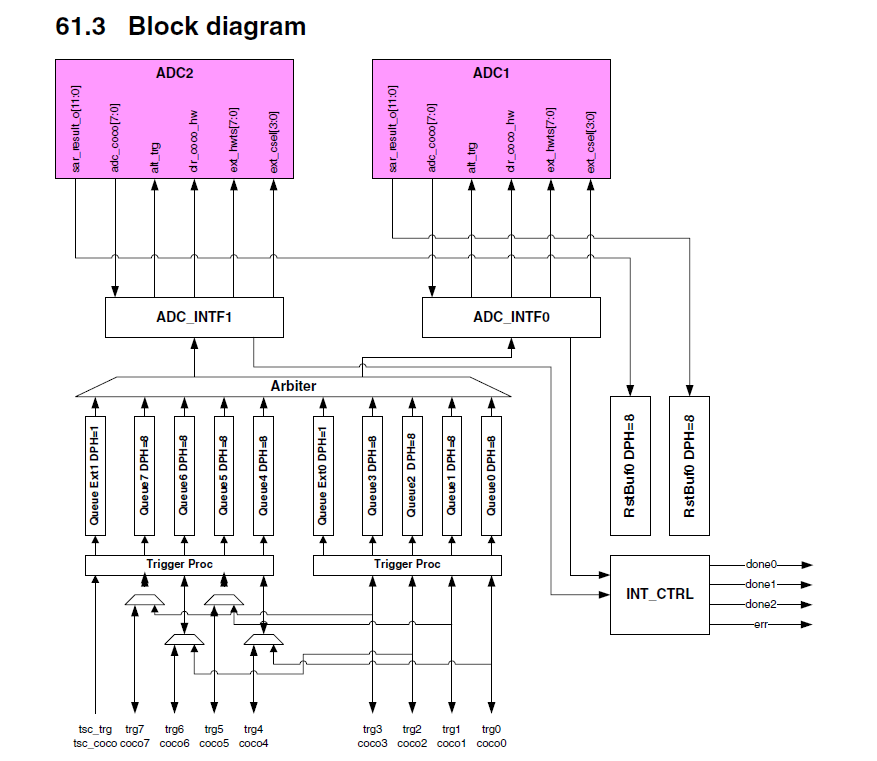

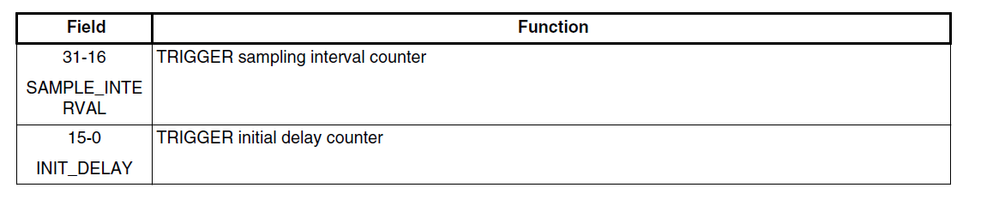

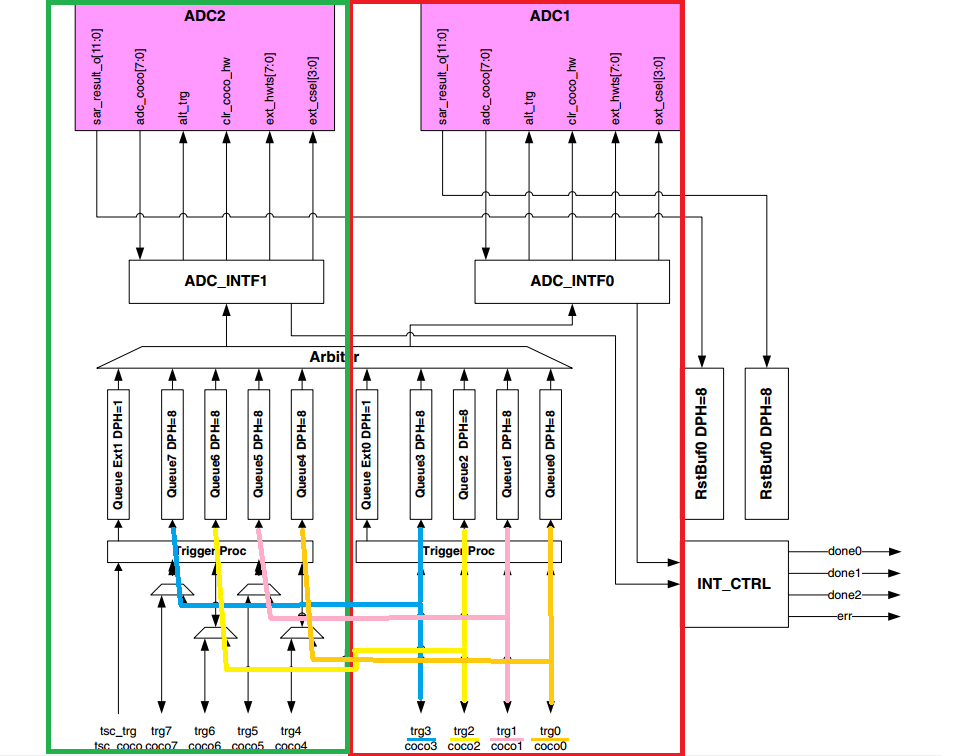

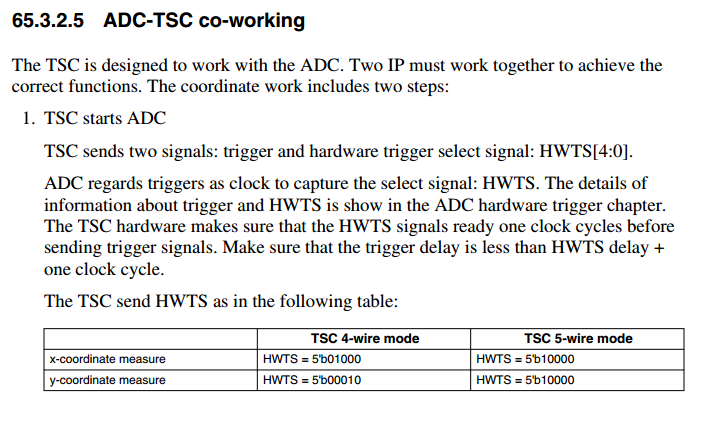

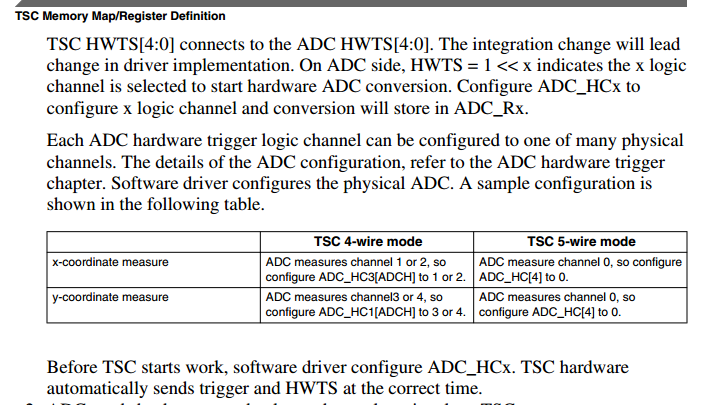

For the ADC_ETC peripheral I'm not sure how the value from HWTSx gets translated to the ADC registers. This overview

looks like every trigger input (trg0 to trg7) can be used for either ADC1 or ADC2 because of the Arbiter - Is that true? To which ADC does the TRIG0_CHAIN_1_0 register belong? And to which ADCx_HCn register does a HWTS0 value of 15 belong?

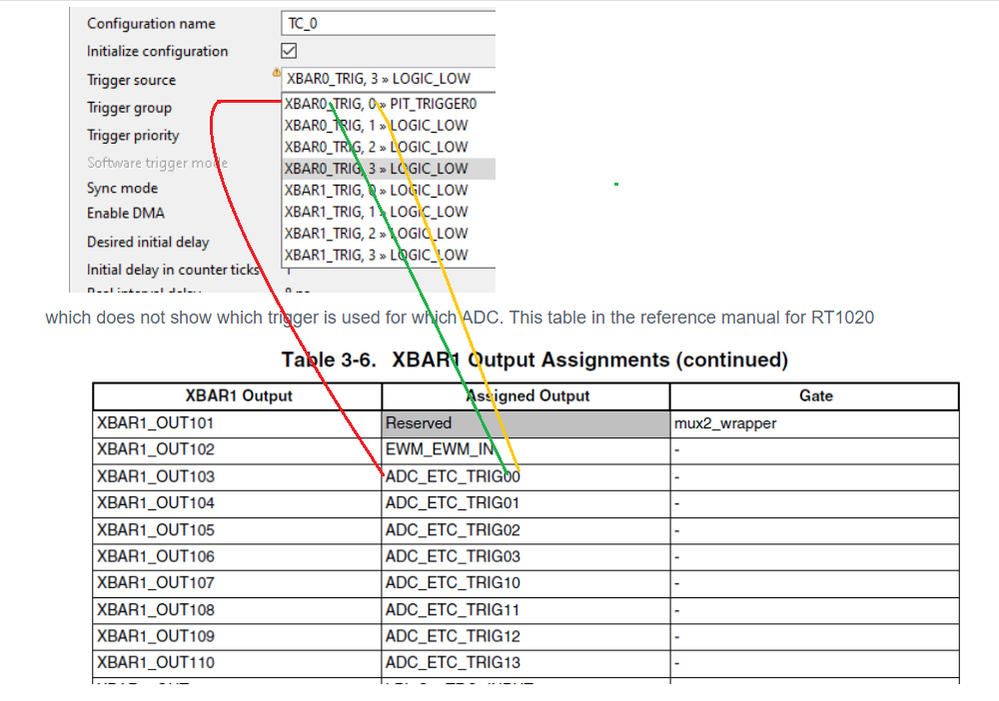

In the peripherals tool i can choose these trigger sources

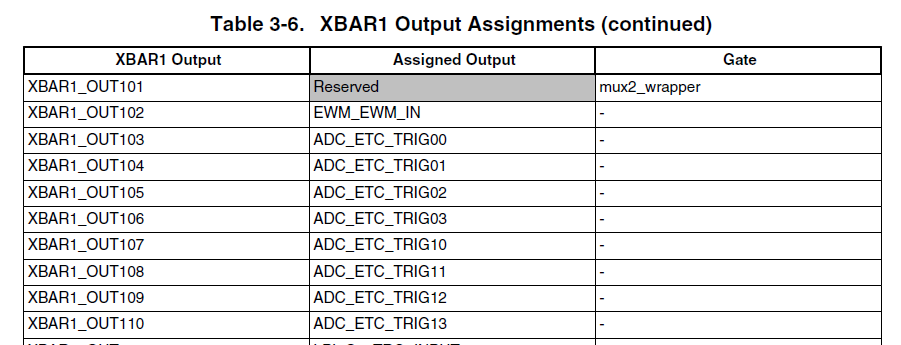

which does not show which trigger is used for which ADC. This table in the reference manual for RT1020

shows that all ADC_ETC Trigger inputs are connected to the XBAR1 peripheral. Why are they named XBAR0 and XBAR1 in MCUXpresso Config Tools?

****

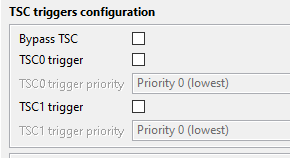

The RT1010 and RT1020 do not have a Touch Screen Controller so I think it would be better understandable if this part

of the ADC_ETC driver will be greyed out or removed for the RT1010 and RT1020 devices and the default values set in code to

.enableTSCBypass = false,

.enableTSC0Trigger = false,

.enableTSC1Trigger = false,

****

Copy from another post as info for MCUXpresso Config Tools Development Team:

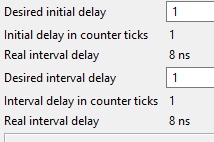

The boxes "Desired initial delay" and "Desired interval delay"

have to be set to at least 1 tick. The reference manual entry to ETC_TRIG0 Counter Register does not mention that the counter has to be set at least to 1 tick.

My question got answered and it is allowed to be 0.

Additional info: The text "Real interval delay" is used for the "Desired initial delay" settings and I think it should be "Real initial delay".

*************

I have posted several other questions about the ADC and ADC_ETC on the IMXRT forum but no answers yet - depending on the answer to Question 5 of this post it is possible that there is something wrong with the warning generation of the ADC peripheral driver.

Kind regards,

Stefan

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

1) You're right about SW trigger it can be selected on all 8 triggers.

2) About ADC conversion control group max number - I don't know whether the feature was available when the component was created, but you are right, the limit should be taken from it.

3) About interconnection of the ADC_ETC:

In the scheme above you can see how I understand it: there are two ADC interface (ADC_INTF0 and ADC_INTF1) which divide whole ADC_ETC into two parts (red and green rectangle).

So e.g.: ADC_INTF0: communicates with ADC1 and its input XBAR triggers are trg0, trg1, trg2, trg3 only.

ADC_INTF1: communicates with ADC2 and its input XBAR triggers are trg4, trg5, trg6, trg7 only.

Exception is SYNC mode that I colored in the scheme at the bottom part in this case trg0 also triggers queue 4, trg1- queue 5, trg2 - queue 6 and trg3 queue 7.

4) Arbiter is there to manage the priority of the triggers.

5) TRIG0_CHAIN_1_0 register is connected to the ADC1 only and means that the source is trg0 and this register has two first queue (chain) items 0 and 1 settings (from 1_0 in register name).

6) Maximum index of ADCx_HCn register is 7 in e.g. RT1050 and so as well HWTS0 = 7 is the maximum value.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

1) You're right about SW trigger it can be selected on all 8 triggers.

2) About ADC conversion control group max number - I don't know whether the feature was available when the component was created, but you are right, the limit should be taken from it.

3) About interconnection of the ADC_ETC:

In the scheme above you can see how I understand it: there are two ADC interface (ADC_INTF0 and ADC_INTF1) which divide whole ADC_ETC into two parts (red and green rectangle).

So e.g.: ADC_INTF0: communicates with ADC1 and its input XBAR triggers are trg0, trg1, trg2, trg3 only.

ADC_INTF1: communicates with ADC2 and its input XBAR triggers are trg4, trg5, trg6, trg7 only.

Exception is SYNC mode that I colored in the scheme at the bottom part in this case trg0 also triggers queue 4, trg1- queue 5, trg2 - queue 6 and trg3 queue 7.

4) Arbiter is there to manage the priority of the triggers.

5) TRIG0_CHAIN_1_0 register is connected to the ADC1 only and means that the source is trg0 and this register has two first queue (chain) items 0 and 1 settings (from 1_0 in register name).

6) Maximum index of ADCx_HCn register is 7 in e.g. RT1050 and so as well HWTS0 = 7 is the maximum value.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Maybe it is too long I have to continue here.

7) Relation of the ADC_ETC signals and XBAR signals in RM:

In the ADC ETC as I said before are two parts ADC_INTF0 and 1.

They have XBAR inputs as triggers. The name of the signal visible in the Pinks tool and also in the ADC_ETC component selection "Trigger source" e.g. XBAR0_TRIG, 3 can be decoded: as XBAR - trigger from XBAR (not from e.g. TSC) 0 - relates to INTF0, TRIG, 3 - trg3.

And this is in the XBAR1 Output Assignments table above = ADC_ETC_TRIG03 (0 and 3 are tuples as we as e.g. 12 is 1 and 2 not twelve) - means 0 - INTF0 and 3 trg3.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

8) For the TSC - it can be nice improvement, but when the component was created, there was only RT1050 with TSC.

9) OK, "Desired initial delay" value can be 0.

But for the Interval it doesn't make sense to start next conversion in chain without delay, it can only abort previous undone conversion or leads into the error interrupt.

10) The other settings when in ADC is selected channel DRIVEN_BY_ADC_ETC has no meaning but should be there specified for the driver of ADC, so let it be. default. ADC peripheral is older and the ADC_ETC is somehow added here to drive it.

I will prepare hot fix of the components ADC_ETC and ADC.

By the way when we creating the component we have to use preliminary manuals and communicate with the HW designer to find how it works, so we have better knowledge base than RM can show, but sometimes the bugs can be in component also.

Hope this help

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy and Jiri,

thank you very much for explaining everything It's a lot clearer for me now!

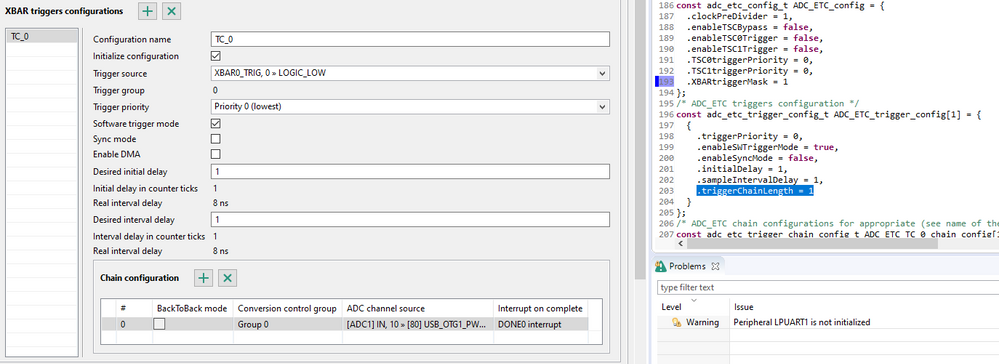

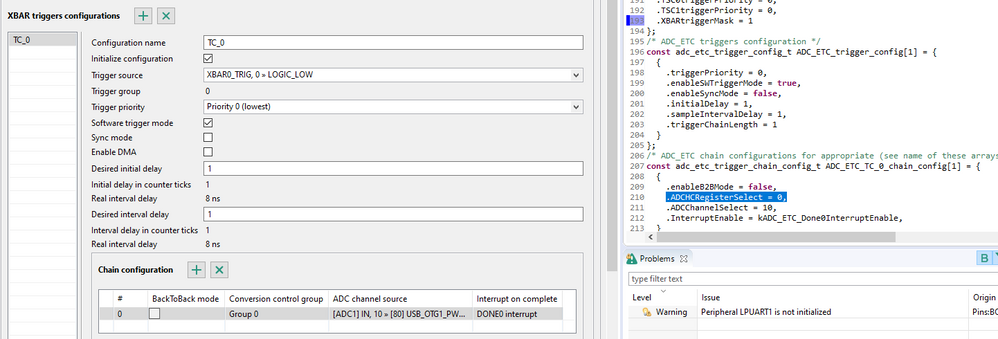

After trying to recreate the adc_etc_software_trigger_conv project with MCUXpresso Config tools I think I found two more bugs for the ADC_ETC driver in peripherals tool:

- If you add one chain element to the XBAR triggers configuration

.triggerChainLength gets set to one - but it has to be zero. In the fsl_adc_etc.h file I found:typedef struct _adc_etc_trigger_config

{

...

uint32_t triggerChainLength; /* TRIG chain length to the ADC. 0: Trig length is 1. ... 7: Trig length is 8. */

...

} adc_etc_trigger_config_t; - Additionally for Conversion control group "Group 0" the variable .ADCHCRegisterSelect gets set to 0

but it should be 1 according to the fsl_adc_etc.h driver:typedef struct _adc_etc_trigger_chain_config

{

...

uint32_t ADCHCRegisterSelect; /* Select relevant ADC_HCx register to trigger. 1U : HC0, 2U: HC1, 4U: HC2 ... */

...

} adc_etc_trigger_chain_config_t;

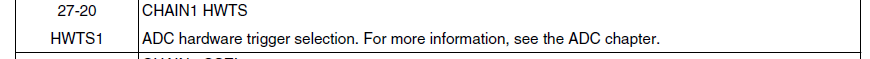

Also I think it would be a good idea to mention the correct values for the HWTS register in the reference manual (RT1020)

instead of referencing the ADC chapter. I can't find a place in the ADC chapter where it is described that a value of HWTS = 1 will select the ADCx_HC0 register.

Kind regards,

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

you're right, thanks for your reporting.

I found this in chapter TSC for better understanding of the HWTS coding:

Now HWTS signal is more clear:

TSC HWTS[4:0] connects to the ADC HWTS[4:0]. The integration change will lead

change in driver implementation. On ADC side, HWTS = 1 << x indicates the x logic

channel is selected to start hardware ADC conversion. Configure ADC_HCx to

configure x logic channel and conversion will store in ADC_Rx.

Logic channel of ADC means the appropriate tuple ADC_HCx and ADC_Rx.

Hope it can helps you also.

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you again Jiri,

yes this information helps. To be honest I did not think about looking in the Reference Manual for the RT1050 as I am currently working with the RT1020.

For other users it might be a good idea to include this information in the Reference Manuals for RT1010 and RT1020 processors too. Maybe you can suggest it to the responsible department.

Kind regards,

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) Is the reference manual correct and every Trigger source can be used as Software Trigger or is the setting in MCUXpresso Config Tools correct and only XBAR0_TRIG 0 can be used as Software Trigger?

-- In general, the reference manual is more reliable than the MCUXpresso Config Tools.

-- Please check the below figure.

2) According to RM, every four external trigger inputs are assigned to each ADC, however, ADC1 and ADC2 are controlled by the same trigger source after enabling Sync Mode.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------