- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- レイヤースケープ

- :

- LS1088A DDR4 driver porting problem

LS1088A DDR4 driver porting problem

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LS1088A DDR4 driver porting problem

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

On LS1088A platform, based on LSDK20.04 version, using onboard particle DDR4 design, the model MT40A512M16LY-075 (64 bit width +8 bit ECC, 4GB in total, 4 pieces of 512M*16 bit DDR4), DDR4 running at 1600MHz, has been produced at present .C file, please see the attachment for details.

The operation process is as follows:

- Imported DDR register value, add the values in the generated ddrtfa_1.c file to the ddr_init.c file in the ATF folder as CONFIG_STATIC_DDR in section 5.2.3 of LSDK,

- Copy all contents of the generated uboot_ddr1.c file to DDR. C file in the u-boot folder,

- 3. Compile ATF and U-Boot folders in Linux interface, then synthesize image and burn it into NOR flash.

Enable static DDR, Open the # define CONFIG_STATIC_DDR

Refer to the RM file 2.2 System Memory Map and set the starting address to 0x0080_8000_0000.

Use DDR Region #2 as recommended, which is DRAM1 in the code, Please refer to attachment 1:

Switch to DRAM1 completely in the BL2 setup file, Please refer to attachment 1:

In setup of BL31, change addr to 80_80000000 and size to 0x100000000//4GB, Please refer to attachment 1:

RCW modifies DDR multiplier to 16, modifies DDR_REFCLK_SEL=0, and selects single-ended DDRCLK input clock,Please refer to attachment 1:

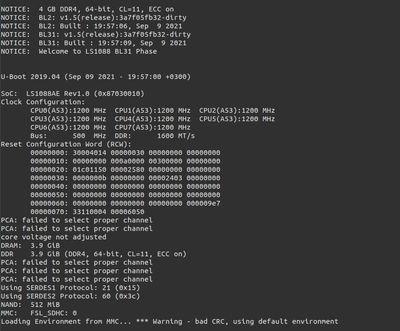

After the compilation is completed, the printed information is Please refer to attachment 1 :

Please check whether the current process is correct and how to modify it. Please help.

Thank you very much!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

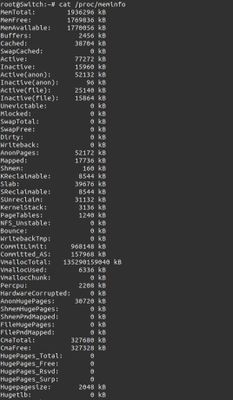

we are having a DDR4 size problem on LS1088a platform. We have 4GB DDR4 on the board. When u-boot starts it is confirmed that board has 4GB DDR4. But when we checked on kernel with cat /proc/meminfo or free commands, it shows that RAM is 2GB. We did tried what @yipingwang post but nothing changed.

Do you have any idea why are we having mismatch DDR size in u-boot and kernel ?

Attached photos you can see the differences.

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

If you want to use fixed DDR registers configurations to initialize DDR controller, you need to define CONFIG_STATIC_DDR in platform_def.h, define function board_static_ddr and structure ddr_cfg_regs in plat/nxp/soc-ls1088/ls1088ardb/ddr_init.c in atf folder. You could refer to plat/nxp/soc-ls1046/ls1046ardb/ddr_init.c.

For example

In plat/nxp/soc-ls1088/ls1088ardb/platform_def.h

#define NXP_DDRCLK_FREQ 100000000

#define NUM_OF_DDRC 2

#define DDRC_NUM_DIMM 2

#define CONFIG_STATIC_DDR

In plat/nxp/soc-ls1088/ls1088ardb/ddr_init.c

#ifdef CONFIG_STATIC_DDR

const struct ddr_cfg_regs static_1600 = {

.cs[0].config = 0x80040322,

.cs[0].bnds = 0x1FF,

.cs[1].config = 0x80000322,

.cs[1].bnds = 0x1FF,

.sdram_cfg[0] = 0xE5004000,

.sdram_cfg[1] = 0x401151,

.sdram_cfg[2] = 0x0,

.timing_cfg[0] = 0x91550018,

.timing_cfg[1] = 0xBAB48E44,

.timing_cfg[2] = 0x490111,

.timing_cfg[3] = 0x10C1000,

.timing_cfg[4] = 0x220002,

.timing_cfg[5] = 0x3401400,

.timing_cfg[6] = 0x0,

.timing_cfg[7] = 0x13300000,

.timing_cfg[8] = 0x1224800,

.timing_cfg[9] = 0x0,

.dq_map[0] = 0x32C57554,

.dq_map[1] = 0xD4BB0BD4,

.dq_map[2] = 0x2EC2F554,

.dq_map[3] = 0xD95D4001,

.sdram_mode[0] = 0x3010211,

.sdram_mode[1] = 0x0,

.sdram_mode[9] = 0x400000,

.sdram_mode[8] = 0x500,

.sdram_mode[2] = 0x10211,

.sdram_mode[3] = 0x0,

.sdram_mode[10] = 0x400,

.sdram_mode[11] = 0x400000,

.sdram_mode[4] = 0x10211,

.sdram_mode[5] = 0x0,

.sdram_mode[12] = 0x400,

.sdram_mode[13] = 0x400000,

.sdram_mode[6] = 0x10211,

.sdram_mode[7] = 0x0,

.sdram_mode[14] = 0x400,

.sdram_mode[15] = 0x400000,

.interval = 0x18600618,

.zq_cntl = 0x8A090705,

.ddr_sr_cntr = 0x0,

.clk_cntl = 0x2000000,

.cdr[0] = 0x80040000,

.cdr[1] = 0xC1,

.wrlvl_cntl[0] = 0x86750607,

.wrlvl_cntl[1] = 0x8090A0B,

.wrlvl_cntl[2] = 0xD0E0F0C,

};

long long board_static_ddr(struct ddr_info *priv)

{

memcpy(&priv->ddr_reg, &static_1600, sizeof(static_1600));

return 0x100000000; /*hardcoded DDR size 4GB*/

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, yipingwang

Refer to ddr_init.c in atf\plat\nxp\soc-ls1046\ls1046ardb, I found that:

size = 0x200000000UL; //8GB

simultaneously in atf\plat\nxp\soc-ls1046\ls1046ardb\platform_def.h, I found that:

#define PLAT_DEF_DRAM0_SIZE 0x80000000 /* 2G */

It seems that PLAT_DEF_DRAM0_SIZE is not required modify when ddr is over 2GB, even though reference manual chapter 2.2 described GPP DRAM Region #1 is 0~2GB at start addr 0x8000_0000

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, no need to modify PLAT_DEF_DRAM0_SIZE.