- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: LS1012A-RDB eMMC flash

LS1012A-RDB eMMC flash

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'd like to set up the eMMC flash on the LS1012A-RDB. I've set the DIP switch to select the eMMC flash on SDHC2 but after booting up I get the error:

mmc1: Controller never released inhibit bit(s).

This message scrolls forever. The SD card on SDHC1 works fine. This is using the LS1012A SDK Rev 0.4

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have discovered the source of my problem. When originally setting up QSPI bank 2, I copied over the RCW and u-boot from QSPI bank 1. These images are from the BHR ASK (I assume). I then loaded u-boot, kernel, and ppa images from the SDK, but not the RCW. Not loading the correct RCW was the source of my problem. After loading the SDK RCW (PBL_0x35_0x08_800_250_1000_default.bin) the eMMC flash came up correctly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have discovered the source of my problem. When originally setting up QSPI bank 2, I copied over the RCW and u-boot from QSPI bank 1. These images are from the BHR ASK (I assume). I then loaded u-boot, kernel, and ppa images from the SDK, but not the RCW. Not loading the correct RCW was the source of my problem. After loading the SDK RCW (PBL_0x35_0x08_800_250_1000_default.bin) the eMMC flash came up correctly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> I've set the DIP switch to select the eMMC flash

What exactly you have done?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

On the LS1012A-RDB there is an LS1012A with 2 SDHC interfaces. SDHC2 is connected to a mux which can select between several different on-board devices using a DIP switch. I have set the switch to:

MUX_SDHC2_S1: 1

MUX_SDHC2_S0: 0

According to the manual this should connect SDHC2 to the onboard eMMC flash. Using the images provided in the SDK I get the error mentioned above.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is the component schematics name printed on the PCB, what are the switches positions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

CPU: LS1012A+ SKT LGA 211

3x MUX: 74CBTLV3253DS

eMMC: MTFC4GACAAAM-1M WT

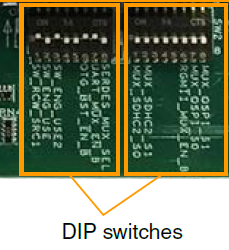

DIP Switches (From left to right on the board)

DIP SW1: 0b11100100

DIP SW2: 0b01000010

In Particular the ones dealing with the eMMC flash are:

MUX_SDHC2_S1: 1

MUX_SDHC2_S0: 0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> MUX_SDHC2_S1: 1

> MUX_SDHC2_S0: 0

To which DIP SW these settings corresponds?

Please provide a clear photo of the switches.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

These are the switches on the board, except the settings are (from left to right):

11100100 01000010

Where 1 is up and 0 is down.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Which configuration is on the photo?

Which switches you have altered?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Shown in the Image:

10100110 00000000

Default that ships with the board:

11100100 00000000

Current board settings:

11100100 01000010

The first two bits of the second switch connect SDHC2 to the eMMC flash, the last two bits of the second switch select booting from the second bank of QSPI flash.

From the default setup that ships with the board I have changed the bit labeled MUX_SDHC2_S1 from 0 to 1, and the bit labeled MUX_QSPI_S0 from 0 to 1.

From the switches in the image the differences are:

SW_ENG_USE: 0 -> 1

UART_MUX_EN_B: 1 -> 0

MUX_SDHC2_S1: 0 -> 1

MUX_QSPI_S0: 0 -> 1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> From the default setup that ships with the board I have changed the bit

> labeled MUX_SDHC2_S1 from 0 to 1, and the bit labeled MUX_QSPI_S0 from 0 to 1.

Please clarify this statement because default setup for these bits is 00.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The defaults are 0 and 0. I changed them both to 1. Changing MUX_SDHC2_S1 should let me use the eMMC flash. Changing MUX_QSPI_S0 lets me boot from the second QSPI flash bank.