- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- lpc1768 watch dog timer

lpc1768 watch dog timer

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I am using LPC1768 watch dog timer, how can we determine to find out the Selectable time period (TWDCLK × 232 × 4) and also i configure mode register to enable the WDT. when we use the RESET bit in WDMOD.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

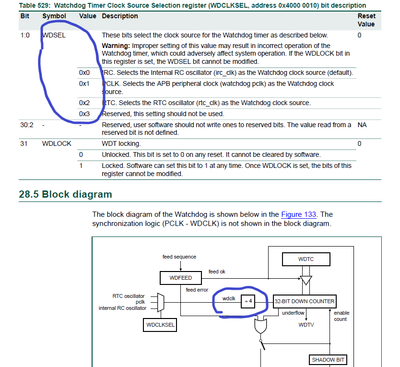

From the following Figs, you can see that the WDT tick source can befrom irc_clk, PCLK and rtc_clk.

The nominal irc_clk is 4MHz , pls refer to section 4.3.1 Internal RC oscillator in UM10360.pdf

The rtc_clk is 1Hz which is generated by 32KHz crystal.

The PCLK for WDT is determined by the selection of register PCLKSEL0[PCLK_WDT], this is the setting, in other words:

PCLKSEL0[1:0]=00 in binary, CCLK/4 is selected.

PCLKSEL0[1:0]=01 in binary, CCLK is selected.

PCLKSEL0[1:0]=10 in binary, CCLK/2 is selected.

PCLKSEL0[1:0]=11 in binary, CCLK/8 is selected.

Pls refer to section 4.7.3 Peripheral Clock Selection registers 0 and 1 (PCLKSEL0 -

0x400F C1A8 and PCLKSEL1 - 0x400F C1AC)

Table 42. Peripheral Clock Selection register bit values

PCLKSEL0 and PCLKSEL1

individual peripheral’s clock

select options

Function Reset

value

00 PCLK_peripheral = CCLK/4 00

01 PCLK_peripheral = CCLK

10 PCLK_peripheral = CCLK/2

11 PCLK_peripheral = CCLK/8,

For the CCLK frequency, pls refer to the PLL0 configuration and the post divider. Pls refer to Fig 7. Clock generation for the LPC176x/5x.

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

From the following Figs, you can see that the WDT tick source can befrom irc_clk, PCLK and rtc_clk.

The nominal irc_clk is 4MHz , pls refer to section 4.3.1 Internal RC oscillator in UM10360.pdf

The rtc_clk is 1Hz which is generated by 32KHz crystal.

The PCLK for WDT is determined by the selection of register PCLKSEL0[PCLK_WDT], this is the setting, in other words:

PCLKSEL0[1:0]=00 in binary, CCLK/4 is selected.

PCLKSEL0[1:0]=01 in binary, CCLK is selected.

PCLKSEL0[1:0]=10 in binary, CCLK/2 is selected.

PCLKSEL0[1:0]=11 in binary, CCLK/8 is selected.

Pls refer to section 4.7.3 Peripheral Clock Selection registers 0 and 1 (PCLKSEL0 -

0x400F C1A8 and PCLKSEL1 - 0x400F C1AC)

Table 42. Peripheral Clock Selection register bit values

PCLKSEL0 and PCLKSEL1

individual peripheral’s clock

select options

Function Reset

value

00 PCLK_peripheral = CCLK/4 00

01 PCLK_peripheral = CCLK

10 PCLK_peripheral = CCLK/2

11 PCLK_peripheral = CCLK/8,

For the CCLK frequency, pls refer to the PLL0 configuration and the post divider. Pls refer to Fig 7. Clock generation for the LPC176x/5x.

Hope it can help you

BR

XiangJun Rong