- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: LPC11U68 ADC linearity problems

LPC11U68 ADC linearity problems

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC11U68 ADC linearity problems

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

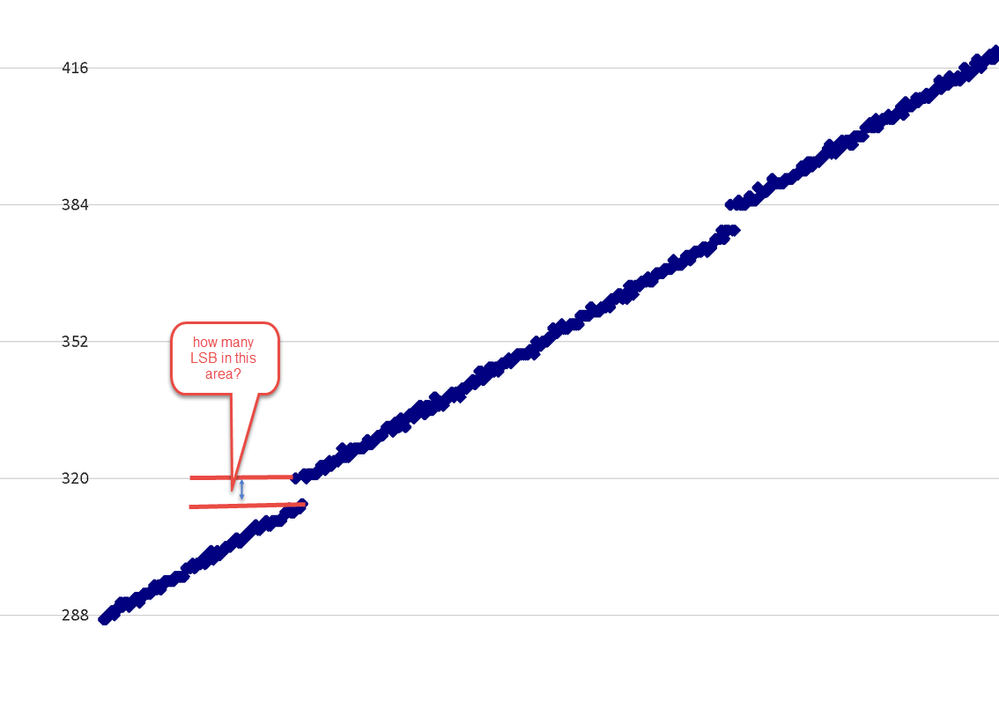

I'm using the LPC11U68, and am seeing rather bad ADC performance. If I run a precision ramp into the input to collect the transfer function, I see that it plateaus at 8 counts before every 64 count boundary, and then jumps up to the boundary. So for example, the ramp will be clean and one to one from 0 to 56, and then the ADC continues to return 56 for 8 steps, and then jumps to 64. Same thing happens at 120 through 128, 184 through 192, etc.

This has been the case with multiple samples of the chip.

Has anyone encountered this? Any ideas? I am running the chip at 3.3V, Ref at 2.5V, and doing the ADC calibration operation per the user manual.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi marcschuman,

Are you convenient to use the ADC to test the fixed voltage, for example 1V on your side? Still use the 64 counts to test it, then send me your excel data.

It also useful to my analysis.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I cannot send you the sample code because it is part of a very large and complicated code base. But here are the key setup lines:

Chip_ADC_Init(LPC_ADC, 99);

Chip_ADC_StartCalibration(LPC_ADC);

while (!(Chip_ADC_IsCalibrationDone(LPC_ADC))) {}

Chip_ADC_SetDivider(LPC_ADC,15);

Chip_ADC_SetupSequencer(LPC_ADC, ADC_SEQA_IDX,

ADC_SEQ_CTRL_CHANSEL(1) |

ADC_SEQ_CTRL_CHANSEL(2) |

ADC_SEQ_CTRL_CHANSEL(4) |

ADC_SEQ_CTRL_CHANSEL(5) |

ADC_SEQ_CTRL_MODE_EOS |

ADC_SEQ_CTRL_HWTRIG_CT32B0_MAT0 |

ADC_SEQ_CTRL_HWTRIG_SYNCBYPASS |

ADC_SEQ_CTRL_HWTRIG_POLPOS |

ADC_SEQ_CTRL_SEQ_ENA);

Chip_ADC_ClearFlags(LPC_ADC, Chip_ADC_GetFlags(LPC_ADC));

Chip_ADC_EnableInt(LPC_ADC, (ADC_INTEN_SEQA_ENABLE));

The counter timer triggers the sequencer at 1 kHz.

The analog input is created by dividing down and filtering a precision waveform created by custom equipment. I cannot get you a scope capture of that waveform at this time. But I can explain that it is a perfect staircase pattern, with the height of each step approximately 200 uV. That is about 1/3 of an lsb for the ADC, which has a Vref of 2.5V. The steps are occurring at 1 kHz and the sampling is at 1 kHz. So there is an uncertainty about where the step edge occurs relative to the sample point, but the step edge is only 200 uV.

I think that if you set up such a test, you will see the same results. This is a standard test of ADC linearity! You can do the same thing with a precision programmable voltage source.

The problem is that this ADC seems to have terrible DNL. I need to know if it is due to a software setup problem, a problem with a batch of chips that we bought, or a problem with all LPC11U68 chips.

Can you provide some actual captured data showing the linearity performance of your ADC?

Thanks!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

HI Marcschuman,

Please tell me how you get your picture:

what is the horizontal axis unit, and vertical axis?

Actually, the slope of the wire is still not change, but it seems the x axis(horizontal axis) time is change, it caused your wire move upword.

So, please tell me how you get these data? save the adc data in the ADC interrupt or the timer interrupt? or any other else?

I do the testing on my LPC11U68 board with a fixed voltage:1.318V, test with multimeter.

Then use a flag in the timer interrupt to indicate the hardware timer happens. And save 100 datas in the while(1) like this:

The converted ADC data also have fluctuation. Tomorrow, I will find a ramp source to test it.

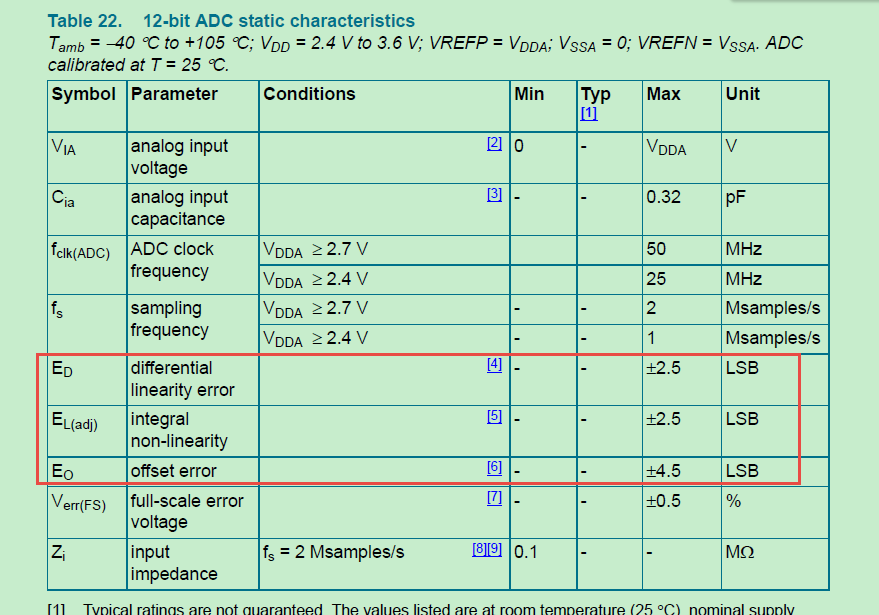

Except the your picture's horizontal axis unit and test method, please also tell me how many LSB on your side in this picutre:

From the datasheet, the LPC11U68 really have the LSB errors:

Please give me more details, I also need to check it with our AE department.

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Here is an image of the collected data. I am converting at 10 ksps. I have a precision analog ramp feeding the input that is stepping at about 1/3 lsb per ADC conversion. You can see that the jumps occur always at 8 counts below a 64 count boundary. That is independent of input offset, sample rate, etc. The ADC seems to have missing codes for the 8 counts prior to each 64 count boundary. Notice also that there is a slope error on each segment. We have seen this exact behavior on multiple samples of the LPC11 MPU. Do you think that the chip should be performing better than this? Is there any kind of software setup problem that could cause this? Or is it possible that we have a bad batch of chips?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi marcschuman,

Please share your ADC sample code(just the ADC code which can reproduce the problem, you don't need to send the whole code), then we can help you to check whether it is the software setup problem.

Please also give me the analog ramp feeding scope waveform, then I will find a similar wave , test it on my side, and try to reproduce your problem.

Waiting for your reply!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Could someone from NXP confirm or dispute this performance data on the LPC11U68? I have a product that depends on this ADC, and it is a huge problem. I will have to redesign the product if this is the actual performance that we will get in production.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi marcschuman,

What the ramp input wave frequency you are using?

And what the ADC convert rate you are configuring?

In the application, the ADC convert rate need at least 5 times or 10 times than the input wave frequency.

You also can provide the ramp input wave picture, and your lpc11u68 adc test code.

Waiting for your reply!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------