- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Is it possible to know if LPC4370 ADC filled a sample?

Hi,

LPC4370 has HSADC.

In the example code, it just enable it and uses DMA to fill the samples.

Chip_GPDMA_PrepareDescriptor(LPC_GPDMA,&adc_lli[0], 30, (uint32_t)&sample, DMA_TRANSFER_SIZE, GPDMA_TRANSFERTYPE_P2M_CONTROLLER_DMA, &adc_lli[1]);

Chip_GPDMA_PrepareDescriptor(LPC_GPDMA,&adc_lli[1], 30, (uint32_t)&sample_2, DMA_TRANSFER_SIZE, GPDMA_TRANSFERTYPE_P2M_CONTROLLER_DMA, &adc_lli[0]);

So is it possible to get a flag or what every time ADC filled a sample?

Like if I use M0 to run ADC. after adc_lli[0] filled sample. Send a flag to M4. And then start adc_lli[1] and fill sample_2.

Hi, JiaAn,

Regarding your question, as you know that it is impossible to read the ADC result from FIFO and write it to memory if you sample the analog channel with 80MSPS, that is why that you have top use DMA to transfer the ADC result from FIFO to memory. Of course, in low sampling frequency, you can use interrupt mode, and in the ISR, you can read the sample from FIFO, and write it to memory.

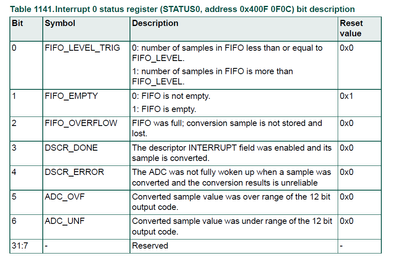

For your question, if you set the INTERRUPT bit in the corresponding Descriptor, when the descriptor is executed, the DSCR_DONE bit in HSADC status0 register will be set, and an interrupt can be triggered.

In other words, when the analog channel in the descriptor has sampled, the DSCR_DONE bit is set, an interrupt is triggered, you can read the sample from FIFO in ISR in low speed sampling frequency.

Hope it can help you

BR

XiangJun Rong