- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: Fluctuations of ADC output for a constant DC input

Fluctuations of ADC output for a constant DC input

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Fluctuations of ADC output for a constant DC input

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using LPC54608J512BD208 microcontroller to design a Protection Relay. I am using ADC in software triggered mode. I run a CTIMER to get an interrupt after every 625 microsecond. On reception of CTIMER interrupt, we trigger sampling of ADC through software trigger. We sample 6 channels ( i.e Channels 0,4,5,6,7,8) of ADC stored in sequence A. On completion of this sequence, ADC raises an interrupt. In ADC interrupt, the channels are read by reading the ADC result registers for each channel.

Observation: We have connected a constant 1.65V DC at input of ADC. There is ripple of hardly 2mV on the input signal as well as VREF of ADC. The output is observed to fluctuates a lot.Ideally, 2048 is the ADC output value expected but this output fluctuates from 1950 to 2090. I have collected 10000 samples during evaluation. Most of the times the output remains closer to 2048 but at times a spike/dip is observed in ADC o/p. All channels behave in the same manner.

We have tried following things in hardware to ensure that the problem is not through hardware:

1) Supplied a constant VREF through a table reference voltage generator IC

2) Connected a 2.9V constant battery at input of ADC.

3) Isolated Anaaog and Digital ground

4) Made analog and digital ground common.

But stilll the issue persists.

Kindly help in resolving this issue.

Thanks & best regards,

Prasanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP,

I am using NXP55s69 Evm. I built adc_dt example and flashed the code.

My adc counts output is not stable.

I have a suspect

in overlay file

output ADC Counts if use External Ref in overlay.

00> - adc@A0000, channel 2: 1304 = 1050 mV

00> ADC reading[5]:

00> - adc@A0000, channel 2: 1300 = 1047 mV

00> ADC reading[6]:

00> - adc@A0000, channel 2: 1300 = 1047 mV

00> ADC reading[7]:

00> - adc@A0000, channel 2: 1306 = 1052 mV

00> ADC reading[8]:

00> - adc@A0000, channel 2: 1297 = 1044 mV

00> ADC reading[9]:

00> - adc@A0000, channel 2: 1308 = 1053 mV

00> ADC reading[10]:

00> - adc@A0000, channel 2: 1294 = 1042 mV

00> ADC reading[11]:

00> - adc@A0000, channel 2: 1294 = 1042 mV

00> ADC reading[12]:

00> - adc@A0000, channel 2: 1304 = 1050 mV

00> ADC reading[13]:

00> - adc@A0000, channel 2: 1298 = 1045 mV

00> ADC reading[14]:

00> - adc@A0000, channel 2: 1304 = 1050 mV

00> ADC reading[15]:

00> - adc@A0000, channel 2: 1316 = 1060 mV

00> ADC reading[16]:

00> - adc@A0000, channel 2: 1303 = 1049 mV

00> ADC reading[17]:

00> - adc@A0000, channel 2: 1315 = 1059 mV

00> ADC reading[18]:

00> - adc@A0000, channel 2: 1300 = 1047 mV

00> ADC reading[19]:

00> - adc@A0000, channel 2: 1303 = 1049 mV

if i configure it as External, should i need to give external input to reference voltage???

If i use internal, adc is not working

00> *** Booting nRF Connect SDK v2.7.0-5cb85570ca43 ***

00> *** Using Zephyr OS v3.6.99-100befc70c74 ***

00> Could not setup channel #0 (-22)

if i configure it as

00> *** Booting nRF Connect SDK v2.7.0-5cb85570ca43 ***

00> *** Using Zephyr OS v3.6.99-100befc70c74 ***

00> Could not setup channel #0 (-22)

what should i do now?

it is all working irrespective of calibration flag

how to configure to get adc counts without fluctuations

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Prasanna,

Can you use the SDK example code and have a test on your board? If the ADC samples fluctuate a lot on your own target board with the same example code, I think that the hardware has issue.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear xiangjun.rong,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear xiangjun.rong,

We have found strange observation during testing of ADC on LPC546 card.

When PE micro debugger is connected, ADC output variations for DC input is high whereas it is considerably low when tested without PE micro debugger (Same is the observation when using SWD connection from LPC11U68 Expresso board to debug LPC546).

Following are the ADC results observed:

Card 1:

| Input Voltage(V) | ADC Channel | With PE Micro | Without PE MIcro | ||

| Min | Max | Min | Max | ||

| 1.65 V (DC) | ADC0_0 | 2014 | 2075 | 2047 | 2051 |

| ADC0_4 | 2020 | 2064 | 2045 | 2054 | |

| ADC0_5 | 2032 | 2058 | 2046 | 2051 | |

| ADC0_6 | 2016 | 2060 | 2048 | 2056 | |

| ADC0_7 | 2021 | 2056 | 2046 | 2052 | |

| ADC0_8 | 2018 | 2051 | 2041 | 2048 | |

Card 2:

| Input Voltage(V) | ADC Channel | With PE Micro | Without PE MIcro | ||

| Min | Max | Min | Max | ||

| 1.65 V (DC) | ADC0_0 | 2010 | 2066 | 2046 | 2052 |

| ADC0_4 | 2035 | 2061 | 2047 | 2054 | |

| ADC0_5 | 2031 | 2062 | 2045 | 2051 | |

| ADC0_6 | 2025 | 2059 | 2050 | 2056 | |

| ADC0_7 | 2019 | 2056 | 2046 | 2052 | |

| ADC0_8 | 2037 | 2049 | 2041 | 2048 | |

Please help in resolving this issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Prasanna,

I have changed the code like:

BOARD_InitPins();

//BOARD_BootClockFROHF48M();

//BOARD_BootClockFROHF96M();

BOARD_BootClockPLL180M();

BOARD_InitDebugConsole();

........

static void ADC_Configuration(void)

{

adc_config_t adcConfigStruct;

adc_conv_seq_config_t adcConvSeqConfigStruct;

/* Configure the converter. */

#if defined(FSL_FEATURE_ADC_HAS_CTRL_ASYNMODE) & FSL_FEATURE_ADC_HAS_CTRL_ASYNMODE

adcConfigStruct.clockMode = kADC_ClockSynchronousMode; /* Using sync clock source. */

#endif /* FSL_FEATURE_ADC_HAS_CTRL_ASYNMODE */

// adcConfigStruct.clockDividerNumber = 1; /* The divider for sync clock is 2. */

adcConfigStruct.clockDividerNumber = 2; /* Rong wrote: The divider for sync clock is 3, the ADC click frequency is 180MHz/3=60MHz, the up-limit is 80MHz. */

#if defined(FSL_FEATURE_ADC_HAS_CTRL_RESOL) & FSL_FEATURE_ADC_HAS_CTRL_RESOL

adcConfigStruct.resolution = kADC_Resolution12bit;

Test1:

when I connect the J12_2 to GND, the sample is all 0 as the following Fig with the code:

Test2:

when I connect the J12_2 to 3.3V, the sample is as the following Fig with the code:

So no problem for the ADC converter even if using PLL.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjunrong,

Thanks for your input!

Why am i getting the fluctuations any idea?

Also please refer my erlier communications with the forum where i have shared the code as well. Can you check if there is any problem in the firmware?

I need one more favor as there is still lockdown in my region and i don't have access to hardware.

I can see that you are checking the output by conncecting either GND or VDD to ADC input. Can you please try following things in the same firmware at LPC546 development board:

1) Core clock at 100 Mhz PLL derived from external crystal

2) Adc clock (1 MHz) derived from core clock

3) DC voltage at ADC input other than reference voltages (lets say 1V or 2V)

4) Create a buffer of 10K samples in firmware and check the maximum and minimum variation in these 10K samples

Thanks & best regards,

Prasanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Prasanna and xiangjun.rong,

I have been following this thread with interest. For reference I am seeing similar issues with the ADC output. As suggested by Prasanna, it would be very helpful to see the results of something other than 0V or Vref as they are not representative 'real world' values. I have been testing using a good quality PSU and resistors to generate the test voltage and see surprising variations in the ADC output.

Kind regards,

Andy

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Prasanna,

I have tested both 48MHz and 24MHz of ADC clock frequency, the result are the same.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi XiangJun Rong,

You might be using sample code from SDK which is operating at internal 48 MHz clock.

I am facing problem while operating the core at 100 MHZ derived from PLL. The ADC output drops considerably.

The 20 usec delay to be provided after PDRUNCFG0 PDEN_ADC0 bit is not there in the drivers provided by MCUXpresso SDK.

So please eveluate the performance at 100 MHz PLL clock stepped down to 1 Mhz and fed to ADC module.

Thank & best regards,

Prasanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Prasanna,

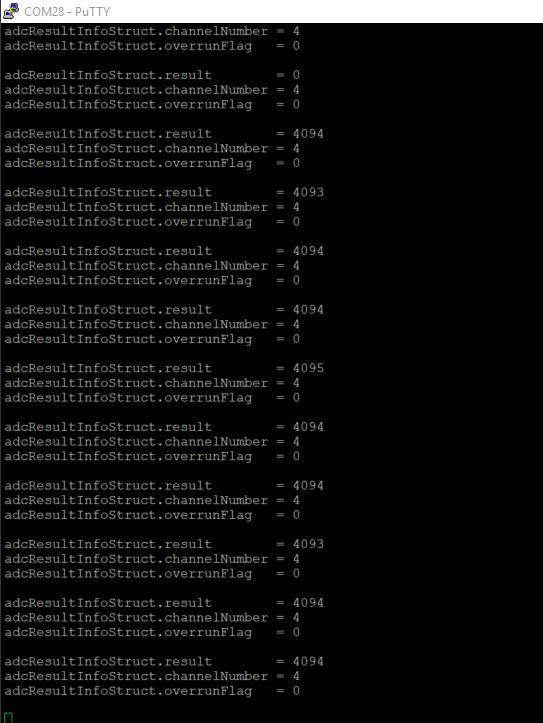

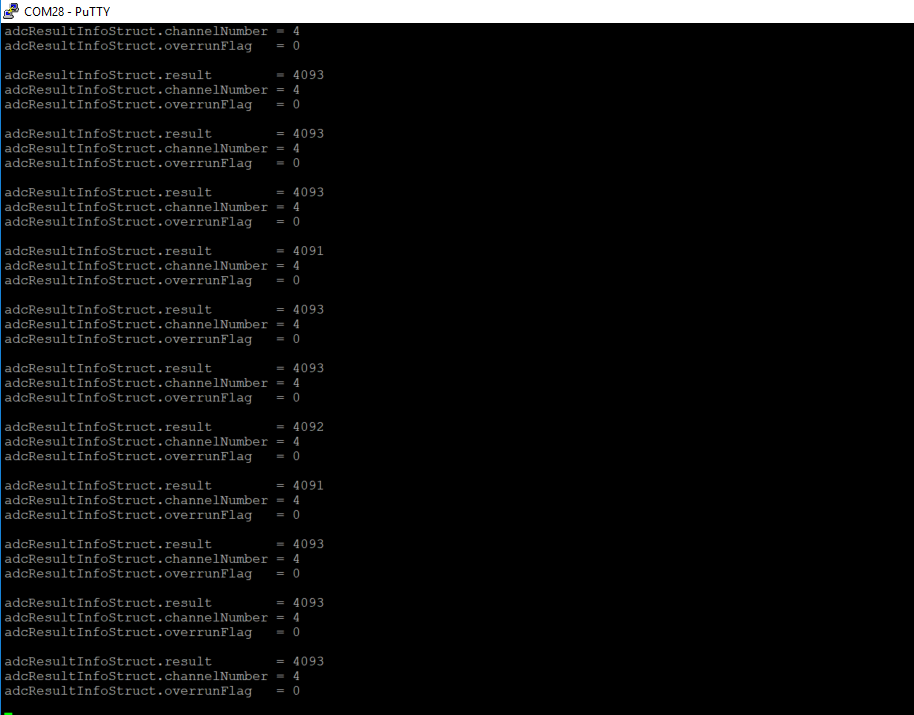

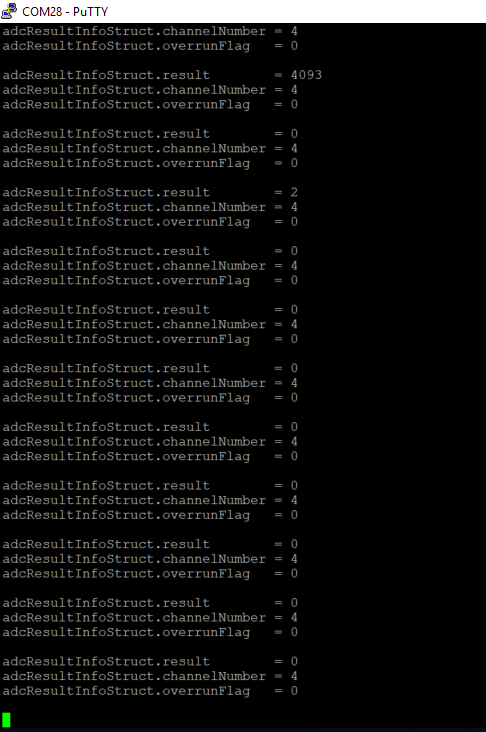

I have used ADC channel 4(J12_2 on LPCXpresso54808 board, PIO0_16/ADC0_IN4) to test the external voltage, when I connect the J12_2 to 3.3V, the sample is from 4091~4093 as the following Fig.

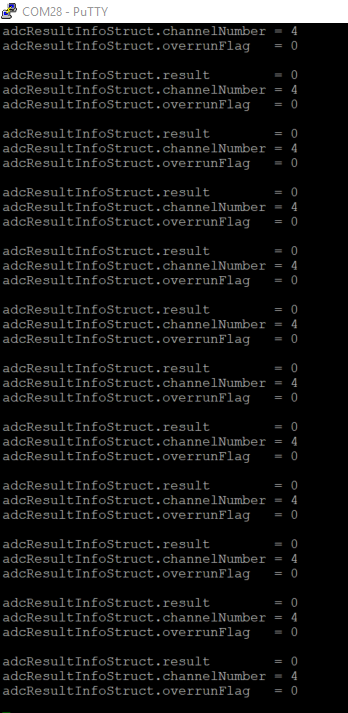

when I connect the J12_2 to GND, the sample is all 0 as the following Fig.

In conclusion, the ADC has not issue.

BR

Xiangjun Rong

Test GND results:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Prasanna,

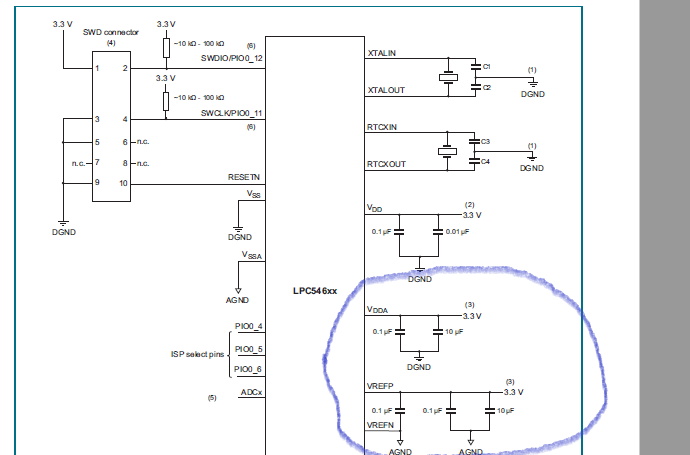

Pls refer to the following fig, you'd better use 10uF and 0.1uF bypass caps to VDDA and VREFP pins, furthermore, you have to have capability to provide enough current to the Vrefp pin.

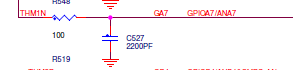

Secondly, I suggest you connect an external capacitor to the analog channel, especially connect 100 ohm resistor and 2.2nF capacitor for each analog channel.

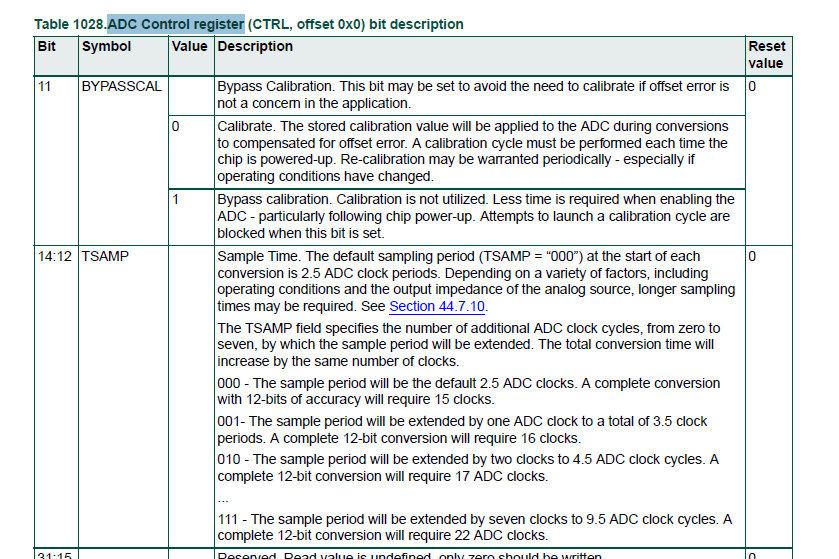

From software, pls try to change the TSAMP bit as 3b'111 for the ADC control register.

Anyway, I think the ADC sample fluctuation from 1950 to 2090 is a bit large.

This is what I can consider, but I do not guarantee it can solve your issue. Pls have a try.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjunrong,

Thanks for your input.

I have tried all the methods suggested above.

1) We have connected 10uF & 0.1uF at VREF pin. I have attached schematic of the same. We have also ensired that the capacitors are close to the VREF pin.

2) We have connected 100 ohms and a 0.1uF at the input of every ADC pin.

3) The TSAMP setting in software is already 7.

But nothing worked.

We are operating microcontroller at 100 MHz. This clock is stepped down to 1 MHz and fed to ADC. ADC is operating in synchronous mode.

Please analyze further and try to simulate the same condition at LPC546 evaluation board.

Thanks & best regards,

Prasanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

2) We have connected 100 ohms and a 0.1uF at the input of every ADC pin.

What would be the resulting input impedance ?

See table 1045 (page 1085) for related requirements. Perhaps you need a buffer opamp.

IMHO the configurable sample time range is objectionable. Other devices allow up to about 500 clock cycles, which eases the requirements for the analog circuitry / buffer amplifier.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Prasanna,

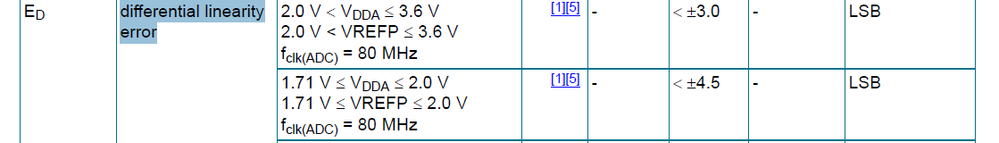

Pls refer to the differential linearity error(ED) spec in the data sheet of LPC5460x.pdf, it is less than +/-3LSB. When you test the same DC voltage, the fluctuation is 2090-1950=40LSB, so it is abnormal.

If you connect the ADC analog channel to GND directly, and sample the channel, what is the result?

BTW, the ADC sample error is related to hardware design, do you have LPC5460x evaluation board and have a test?

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjunrong,

Thanks for your input!

1) Yes. The observation is indeed strange and unacceptable.

2) I have not connected ground directly to ADC input. Also i may not be able to perform this now because of the lockdown in my region.

3) I don't have eveluation board. Otherwise i would have got direct comparision on it. That's why requesting your support in this issue.

Please try to simulate this issue on the evaluation board at your end.

Also could debugger or IDE play a role in this?. I am using PE Multilink for debugging.

Thanks & best regards,

Prasanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi xiangjunrong,

Were you able to simulate the issue in evaluation board of lpc54608.

Also, please check the operation of adc with core clock raised to 100MHz through PLL.

Thanks & best regards,

Prasanna