- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- About LPC1768 programming problem

About LPC1768 programming problem

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

About LPC1768 programming problem

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Sir:

We are a third-party programmer manufacturer.

Please help about LPC1768 programming issues.

P2[10] pull low of our circuit, using SWD IAP programming

When copy RAM to Flash / erase, if CCLK is not set according to the current frequency, will there be any problems in programming?

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Sir:

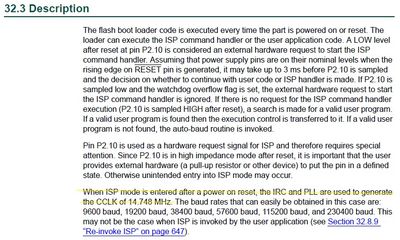

We refer to the document "UM10360.pdf" LPC176x/5x User Manual 32.3 Description.

There is a description "When entering ISP mode after power-on reset, IRC and PLL are used to generate 14.748MHz CCLK", as shown in the figure below.

When P2[10] is pulled low, CCLK is set to 4000kHz, after using SWD IAP programming, power-on reset again, will it affect the programming result?

Is it feasible to set CCLK to 4000kHz? Do you have a recommended setting?

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have checked the data sheet of LPC17xx, but I have not found out the spec of the required CCLK frequency when you call the IAP function.

How about configuring the CCLK as 14.748MHz using PLL before you call IAP function?

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Thanks for your reply.

How about that? I have a idea.

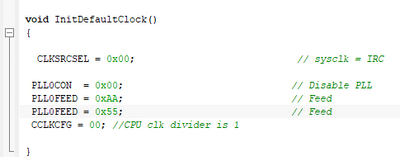

After power cycle, initial the system clock to default 4Mhz in my "ram application"(run app in lpc1768 ram), whatever device into application mode or ISP mode.

I can make sure that the current system clock is default and I can know exact CCLK to send for "Copy RAM to Flash" and "Erase sector".

Here is my initialize code for clock.

By the way, send a incorrect CCLK or is not current system clock. What will happen for device? Any risk?

In my experience, I sent a incorrect CCLK in my side, the flash data will be wrong after flash programming.

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

This is my opinion, when you erase or program flash, the driving flash clock must be in a range, out of the range, there is issue to erase/program flash. But I can not get the flash clock spec now.

In the IAP function to erase/program flash, the CPU Clock Frequency CCLK must be high enough so that the flash driver in IAP can divide it to an appropriate frequency for flash. If CCLK is too low, the flash driver can not get the appropriate frequency by a divider.

You can write the PLL register so that you can get 14.748MHz, you can output the clock to the CLKOUT pin so that you can test via a scope.

Hope it can help you

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

For LPC1768, the P2[10] pin is multiplexed P2[10]/EINT0/NMI, furthermore, it is an ISP pin, in other words, if you connect external pull-down resistor to the pin, after you download application code to the flash of LPC1768, after Reset, the LPC1768 will enter ISP mode, it can not execute application code. But I think the pull-down resistor on the P2[10] does not take effect on programming LPC1768 with JTAG.

In general, user has to connect the P2[10] pin to a hardware button, when user wants to enter ISP mode to download application via uart, he can press the button so that the P2[10] is low, the LPC1768 enters ISP mode after Reset. When user wants to execute application code, just keep the button in release state, the P2[10] will be high, application code will be executed after Reset.

Hope it can help you

BR

XiangJun Rong