- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Software Development Kit

- :

- Round-off error in PLL frequency calculation

Round-off error in PLL frequency calculation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Round-off error in PLL frequency calculation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

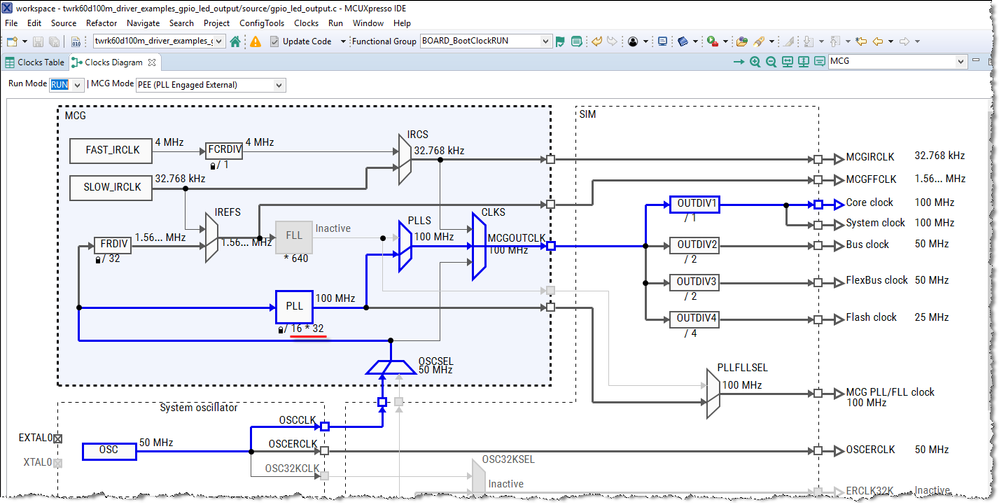

In MK60DN256VLL10, I'm using external 50MHz clock in PEE mode with divide by 13 and multiply by 26 to obtain 100MHz System clock and Core clock. I couldn't find another way to get 100MHz.

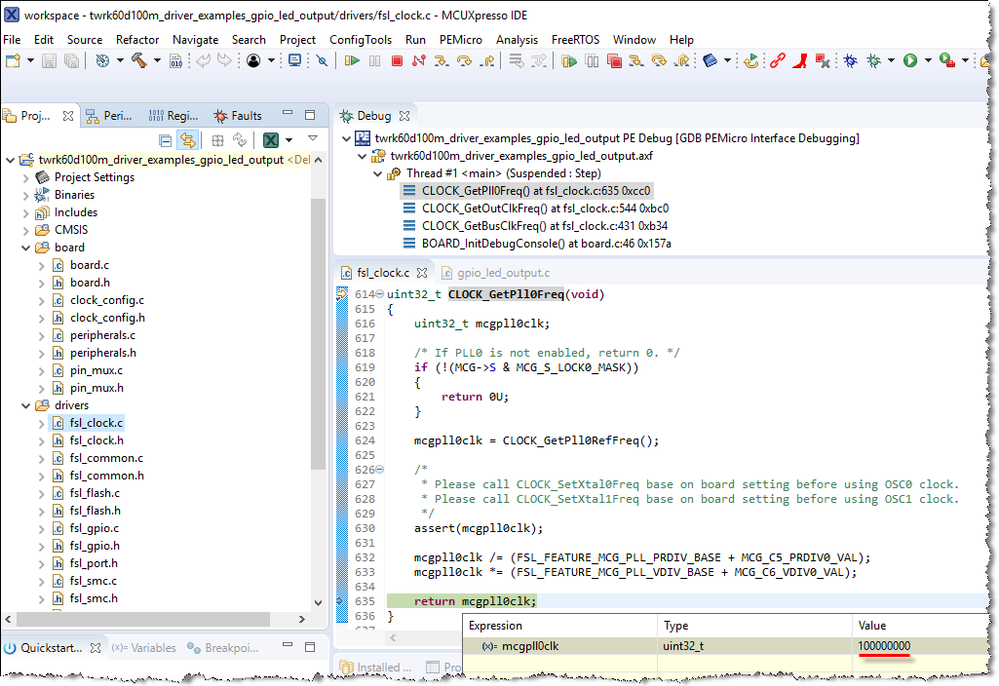

Issue is Kinetis SDK code generates frequency as 99,999,978 instead of 100,000,000 which causes problems in FTM functionality.

I think the real issue is in fsl_clock.c,

.......................

uint32_t CLOCK_GetPll0Freq(void)

{

uint32_t mcgpll0clk;

/* If PLL0 is not enabled, return 0. */

if (!(MCG->S & MCG_S_LOCK0_MASK))

{

return 0U;

}

mcgpll0clk = CLOCK_GetPll0RefFreq();

/*

* Please call CLOCK_SetXtal0Freq base on board setting before using OSC0 clock.

* Please call CLOCK_SetXtal1Freq base on board setting before using OSC1 clock.

*/

assert(mcgpll0clk);

mcgpll0clk /= (FSL_FEATURE_MCG_PLL_PRDIV_BASE + MCG_C5_PRDIV0_VAL);

mcgpll0clk *= (FSL_FEATURE_MCG_PLL_VDIV_BASE + MCG_C6_VDIV0_VAL);

return mcgpll0clk;

}

...................

CLOCK_GetPll0RefFreq() sets mcgpll0clk to 50,000,000 which is correct. After we divide by 13 and multiply by 26, expectation is mcgpll0clk will be set to 100,000,000. Instead, it gets set to 99,999,978. This rounding off error creates problem elsewhere. For instance, in fsl_ftm.c,

.....

switch (mode)

{

case kFTM_EdgeAlignedPwm:

case kFTM_CombinedPwm:

base->SC &= ~FTM_SC_CPWMS_MASK;

mod = (ftmClock / pwmFreq_Hz) - 1;

break;

.....

Here, I set pwmFreq_Hz to 25MHz and expectation is ftmClock = 50MHz so that mod is 1. Since ftmClock gets set to half of 99,999,978, mod gets set to 0 instead of 1 and it breaks FTM functionality.

For now, I have hacked the code and restructured it so that 26 gets divided by 13 first and the result is then multiplied to mcgpll0clk to get clean 100MHz. I'm not sure how the PLL is designed in hardware and if this change accurately models the hardware.

Please let me know if there is an alternate way to avoid rounding off error or fix the code in the next release.

Regards,

Satish

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Satish,

Thank you for the report, I'll inform the SDK team about this.

Sorry for the inconvenience we bring you!

Please try to modify the PRDIV=16 and VDIV=32 manually. Then the SDK function will get clean 100MHz.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------