- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Software Development Kit

- :

- Direct FRDM-KL43Z4 FlexIO register configuration

Direct FRDM-KL43Z4 FlexIO register configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m trying to write program that generates PWM output on PTD2 (J2-4) and RED LED is continually blinking .

My problem is with FlexIO register access. On the first “FLEXIO->…” instruction the program corrupts probably with unsupported NMI.

Sample program

// ========== RED LED Configuration

SIM->SCGC5 |= 0x2000; // enable clock to Port E

PORTE->PCR[31] = 0x100; // make PTE31 pin as GPIO for RED LED

PTE->PDDR |= 0x80000000; // make PTE31, output pin

PTE->PDOR |= 0x80000000; // turn off LED

// ========== FlexIO Configuration

FLEXIO->CTRL |= 0x0; // FlexIO disable

SIM->SCGC5 |= 0x80000000; // enable FLEXIO clock

PORTD-> PCR[2] = 0x600; // make PTD2 FXIO0 D2 (Alt. #6)

// PTD->PDDR |=0x4 ; // ???

FLEXIO->TIMCTL[0] |= 0x430202;

// Timer CTL: TRGSEL=0, TRIGPOL=0, TRGSRC=1,PINCGG=3, PINSEL=2, PINPOL=0, TIMOD=2

FLEXIO->TIMCFG[0] |= 0x0; // Timer 0 Config.

FLEXIO->TIMCMP[0] |= 0x58;

FLEXIO->CTRL |= 0x1;

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks

It is working but only with FlexIO clock = MCGPCLK ( b01).

I tried also options with FlexIO clock = MCGIRCLK (which by default is 8MHz and can be divided), but there is no output on selected Timer output (PTD2).

Is it somehow connected to gated clock, if yes how to enable this clock ?

Regards

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Rong

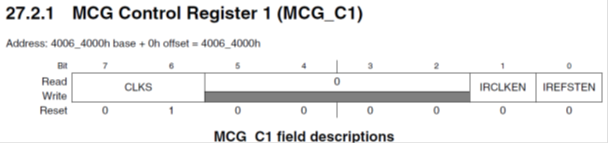

The problem with FlexIO clock = MCGIRCLK was solved there is MCG_C1 register with IRCLKEN field which enables IRC8M module.

Thanks for your helpful and fast response support.

Hope to hear from you with my next questions.

BR

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Shaul,

I suppose you have to enable the FlexIO gated clock before you access any FlexIO register. For your case, pls put the line

SIM->SCGC5 |= 0x80000000; as first line.

In other words, use the code like:

// ========== FlexIO Configuration

SIM->SCGC5 |= 0x80000000; // enable FLEXIO clock

FLEXIO->CTRL |= 0x0; // FlexIO disable

PORTD-> PCR[2] = 0x600; // make PTD2 FXIO0 D2 (Alt. #6)

// PTD->PDDR |=0x4 ; // ???

FLEXIO->TIMCTL[0] |= 0x430202;

// Timer CTL: TRGSEL=0, TRIGPOL=0, TRGSRC=1,PINCGG=3, PINSEL=2, PINPOL=0, TIMOD=2

FLEXIO->TIMCFG[0] |= 0x0; // Timer 0 Config.

FLEXIO->TIMCMP[0] |= 0x58;

FLEXIO->CTRL |= 0x1;

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Rong

I forgot to inform you that I’m using FRDM-KL43Z4 board with KDS v3.2 and KSDK v2.

I think that the problem is that with the “Build” process which generates hard fault during run time.

Unfortunately I’m not skilled enough to handle this kind of problems.

BR

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

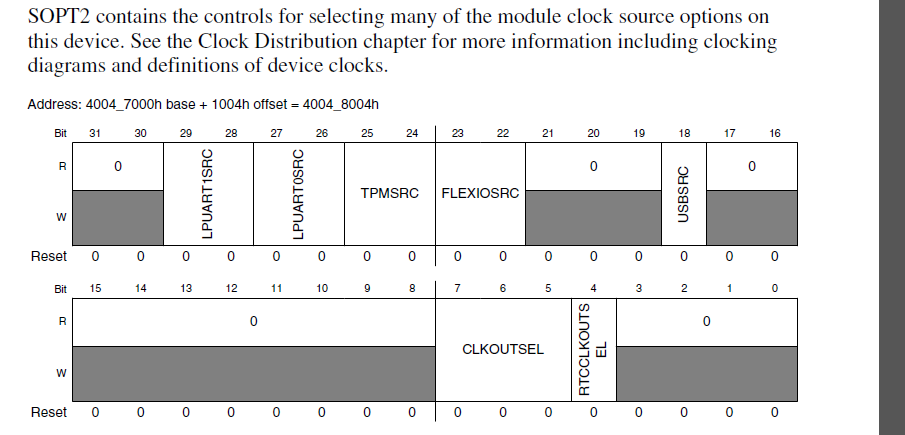

Hi, Shaul,

I am sorry. I think you have to select the FlexIO clock source with FLEXIOSRC bits in SIM_SOPT2, the default is 2b'00, which disable any clock.

BR

Xiangjun Rong

FlexIO Module Clock Source Select

Selects the clock source for the FlexIO transmit and receive clock.

00 Clock disabled

01 IRC48M clock

10 OSCERCLK clock

11 MCGIRCLK clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks

It is working but only with FlexIO clock = MCGPCLK ( b01).

I tried also options with FlexIO clock = MCGIRCLK (which by default is 8MHz and can be divided), but there is no output on selected Timer output (PTD2).

Is it somehow connected to gated clock, if yes how to enable this clock ?

Regards

Shaul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I suppose that you do not enable PORTD gated clock because of using PORTD-> PCR[2] = 0x600;, pls use the code:

SIM->SCGC5 |= 0x3000; //enable PORTE and PORTD

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi;

Doesn’t solve the problem. Ports D, E and FlexIO are clocked still Hard Fault interrupt

Shaul