- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: increase in current consumption after POR

increase in current consumption after POR

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

increase in current consumption after POR

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

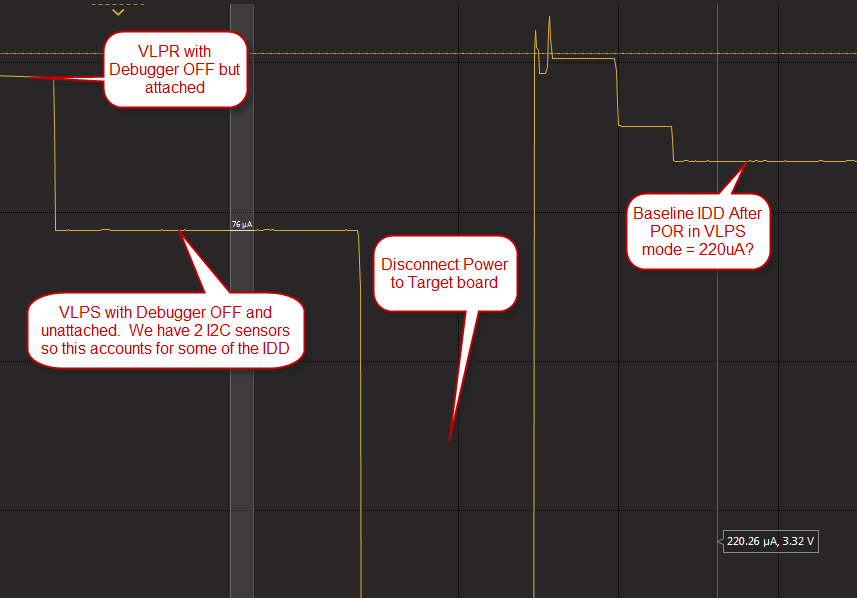

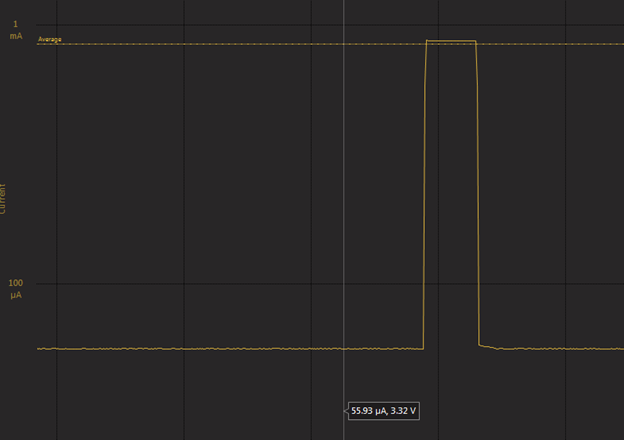

I am having an issue with IDD on a KL03. We are seeing VERY STRANGE behavior in which we have simplified the application to simplify/track down the issue. One of the big issues I am seeing is that after I program the Device(custom hardware) with a J-LINK I disable the debugger and unplug the cable. The system shows what I would expect after turning off/disconnecting the debugger cable. I then Power Cycle the device and all of a sudden my base line current consumption jumps from 76uA to 220uA? What is going on here? This is utterly baffling why a POR which should execute the same code causes the system to jump from 76uA to 220uA? This is a critical situation and a major roadblock on this project. Does anyone have an idea what is going on here?

Setup:

Run Mode: 2MHz VLPR

Sleep Mode: VLPS

Using KDS3.0 KSDK1.3

I have attached a power profile screenshot.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

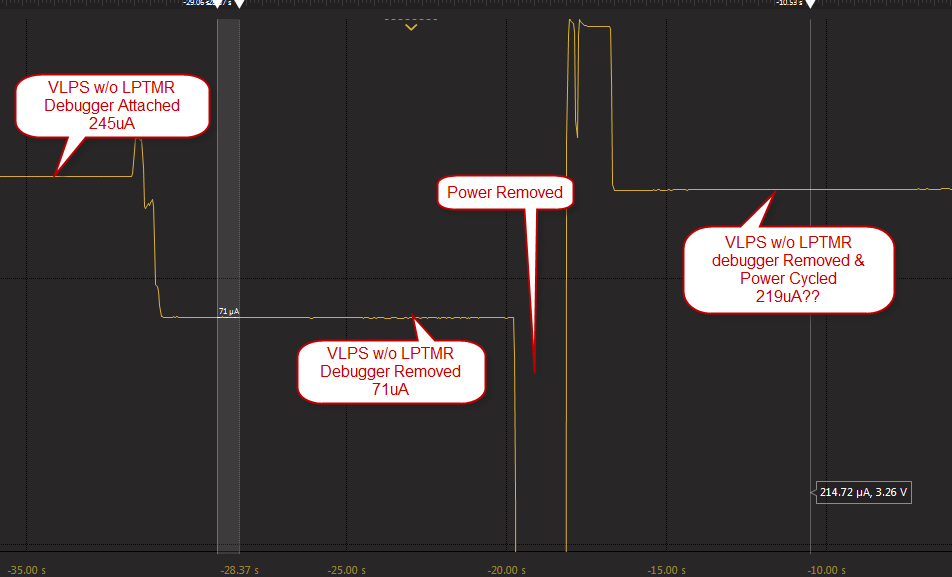

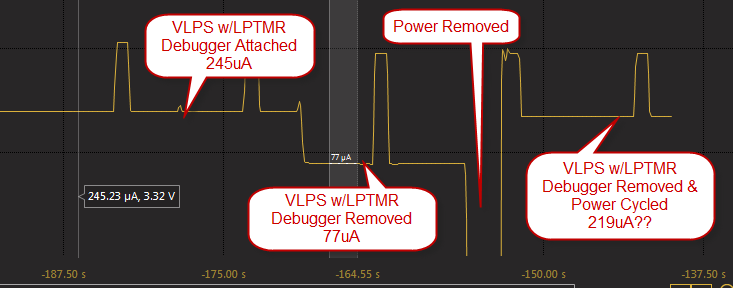

I have taken further steps to narrow the scope on this matter. I have removed all other components to where the PCB only has the KL03 and some bypass caps. We are still seeing the same issue in that after the Debugger has been removed and the device is Power Cycled we see a significant increase in IDD. After the Debugger has been removed the device can be RESEST via the RESET line and maintains a consistent IDD but as soon as it is Power Cycled the IDD increases significantly. We are seeing what I would consider excessive current also in VLPS mode in which we are seeing with all peripherals disabled 71uA compared to what we would have expected ~2uA. Lastly when we enabled the LPTMR we are seeing an increase by ~6uA. Does anyone have any insight into this? It is rather clear that the device is getting into VLPS mode as there is a clear transition from VLPR to VLPS in the Power Profile but it is still what we would consider excessive. See most current Power Profiles below that show the increase IDD currents after a Power cycle and comparing with and without LPTMR.

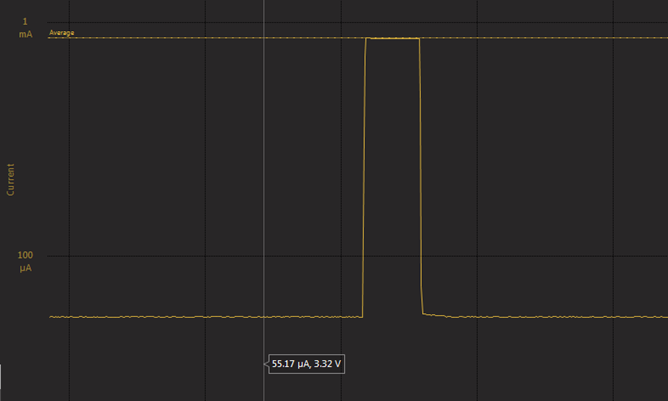

Power Profile W/O LPTMR in VLPS mode. Notice IDD jump from 71uA to 219uA after Power Cycle...?

Power Profile with LPTMR in VLPS mode Notice again increase in baseline VLPS IDD after Power Cycle.

Regards,

Frank

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Frank,

if we suppose, that the code is running properly, please try check the output pin's state when debugger removed and power consumption = 77uA and in the second state after POR - IDD = 219uA. It could be such difference which could point to reason of this higher current consumption.

The next option is to read this AN and compare the settings of MCU:

http://cache.freescale.com/files/32bit/doc/app_note/AN4503.pdf

Best Regards,

Stano.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Stanis,

I don't see how there would be any difference in PIN states that could account for this sharp of a rise when there is nothing else on the PCB except the KL03? Secondly all the Pins are initialized in an init() function that is called every time the MCU comes alive. From what you are indicating somehow this function would be setting pins differently when it is executed during Debugging than when it is ran in a stand-alone fashion which would be even more troubling/concerning...we do disable the Debug Pins when the device goes to sleep.

Secondly I do believe there may be some sort of strange thing going on in firmware as to whether or not it is truly getting into VLPS BUT this would not account for a RISE in IDD after it has initially been programmed executes and then is power cycled and the current rises sharply...

Regards,

Frank

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

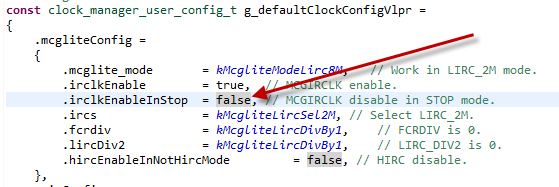

I have done further evaluation of this scenario. Another strange thing that I have observed with the KL03 is that I can change the setting for whether the LIRC Oscillator is Enabled/Disabled in STOP mode. Before I go into VLPS I can clearly see the bit is either SET/CLEARED as to whether this should occur and I don't see any difference in the actual IDD on the board that I ONLY have the KL03 and a couple of Bypass caps. I would hope that I should see the LIRC when it is disabled in STOP/VLPS produce about a 27uA difference which should be clearly observable but I see the same IDD whether it is Enabled/Disabled in STOP mode?

I will package up the project that is producing this it is very simple and makes use of KDS3.0 and KSDK1.3.

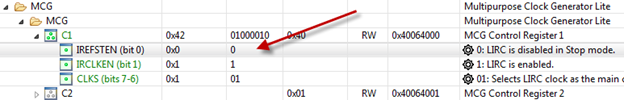

- Configuration to TURN OFF LIRC in STOP Mode

See the BIT get cleared...

Energy Profile with LIRC Clock supposedly Turned OFF in VLPS.

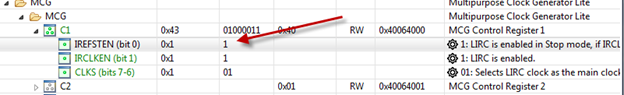

Test with Enabling the LIRC in Stop Mode:

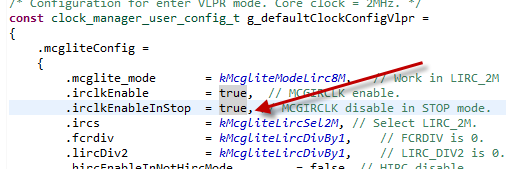

- Configuration to keep LIRC ON in STOP Mode

See the Bit get set...

Energy Profile with LIRC Kept On during VLPS is same as when it was supposed to be Disabled?